Pci express advanced error header, Log - adverr_log1, Log - adverr_log2 – Intel CONTROLLERS 413808 User Manual

Page 361: Transaction header log for pci express error, Address translation unit (pci express)—intel, Bit default description, Intel

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

361

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

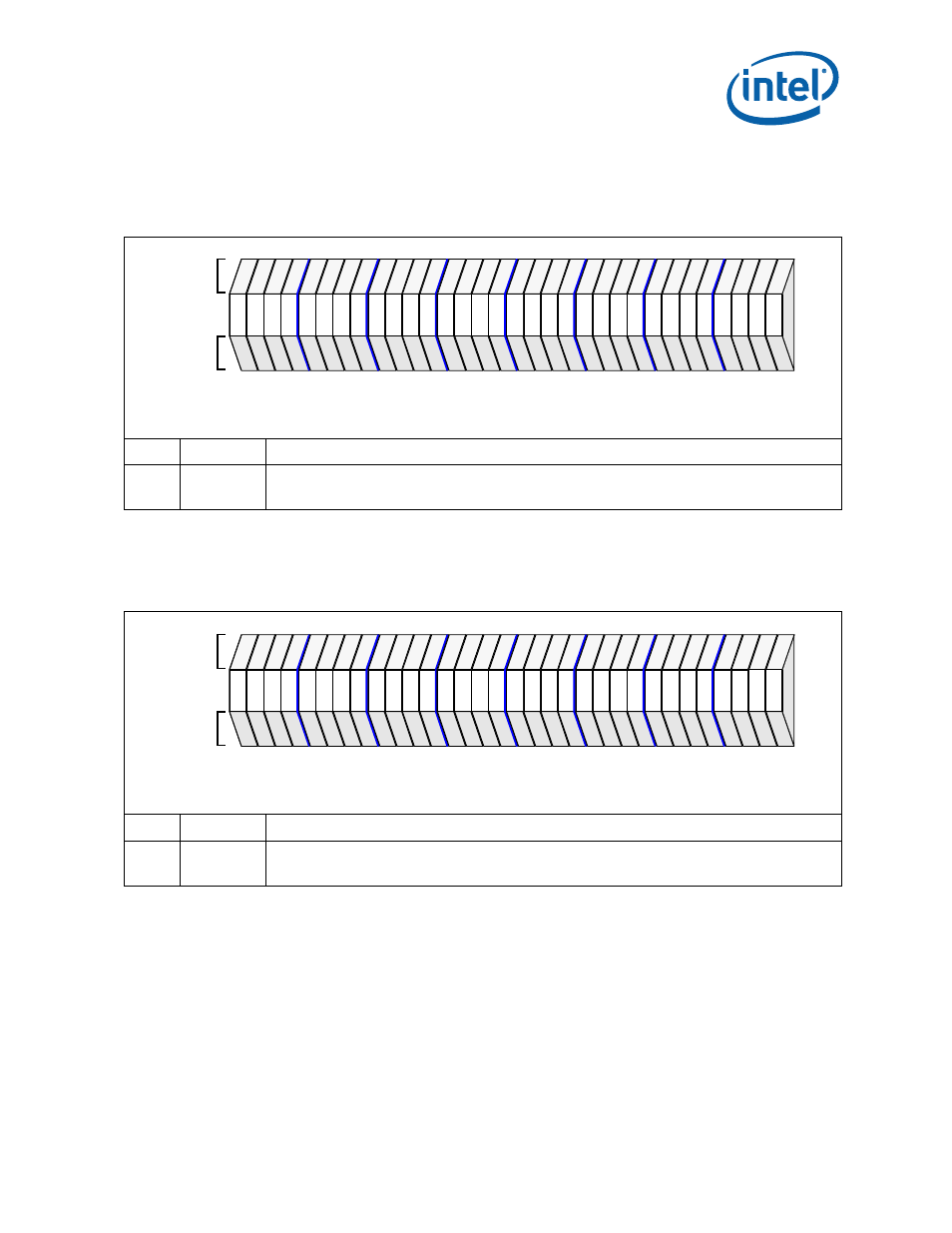

3.17.77 PCI Express Advanced Error Header Log - ADVERR_LOG1

Transaction header log for PCI Express error.

3.17.78 PCI Express Advanced Error Header Log - ADVERR_LOG2

Transaction header log for PCI Express error.

Table 217. PCI Express Advanced Error Header Log - ADVERR_LOG1

Bit

Default

Description

31:0

0

2nd DWord of the Header for the PCI Express packet in error.

Once an error is logged in this register, it remains locked for further error logging until the time the

software clears the status bit that cause the header log i.e. the error pointer is rearmed to log again.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

S S S

S

S S S S

S S S

S

S S S

S

S S S

S

S S S

S

S S S

S

S S S S

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+120H

Table 218. PCI Express Advanced Error Header Log - ADVERR_LOG2

Bit

Default

Description

31:0

0

3rd DWord of the Header for the PCI Express packet in error.

Once an error is logged in this register, it remains locked for further error logging until the time the

software clears the status bit that cause the header log i.e. the error pointer is rearmed to log again.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

S S S

S

S S S S

S S S

S

S S S

S

S S S

S

S S S

S

S S S

S

S S S S

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+124H