4 register definitions, Table 433. smbus register summary, 1 smbus controller command register - sm_cmd – Intel CONTROLLERS 413808 User Manual

Page 655: 1 smbus controller command register — sm_cmd, 433 smbus register summary, 434 smbus controller command register — sm_cmd

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

655

SMBus Interface Unit—Intel

®

413808 and 413812

12.4

Register Definitions

This section provides a summary descriptions of all the SMbus registers. The SMBus

Interface Unit has eight registers which are accessible from the SMBus interface only.

Firmware cannot access these registers on 4138xx.

12.4.1

SMBus Controller Command Register — SM_CMD

This is the Command Register. All accesses from the SMBus port are initiated by writing

to this register. While a command is in progress, all future writes or reads are NACKed

by the 4138xx to avoid having registers overwritten.

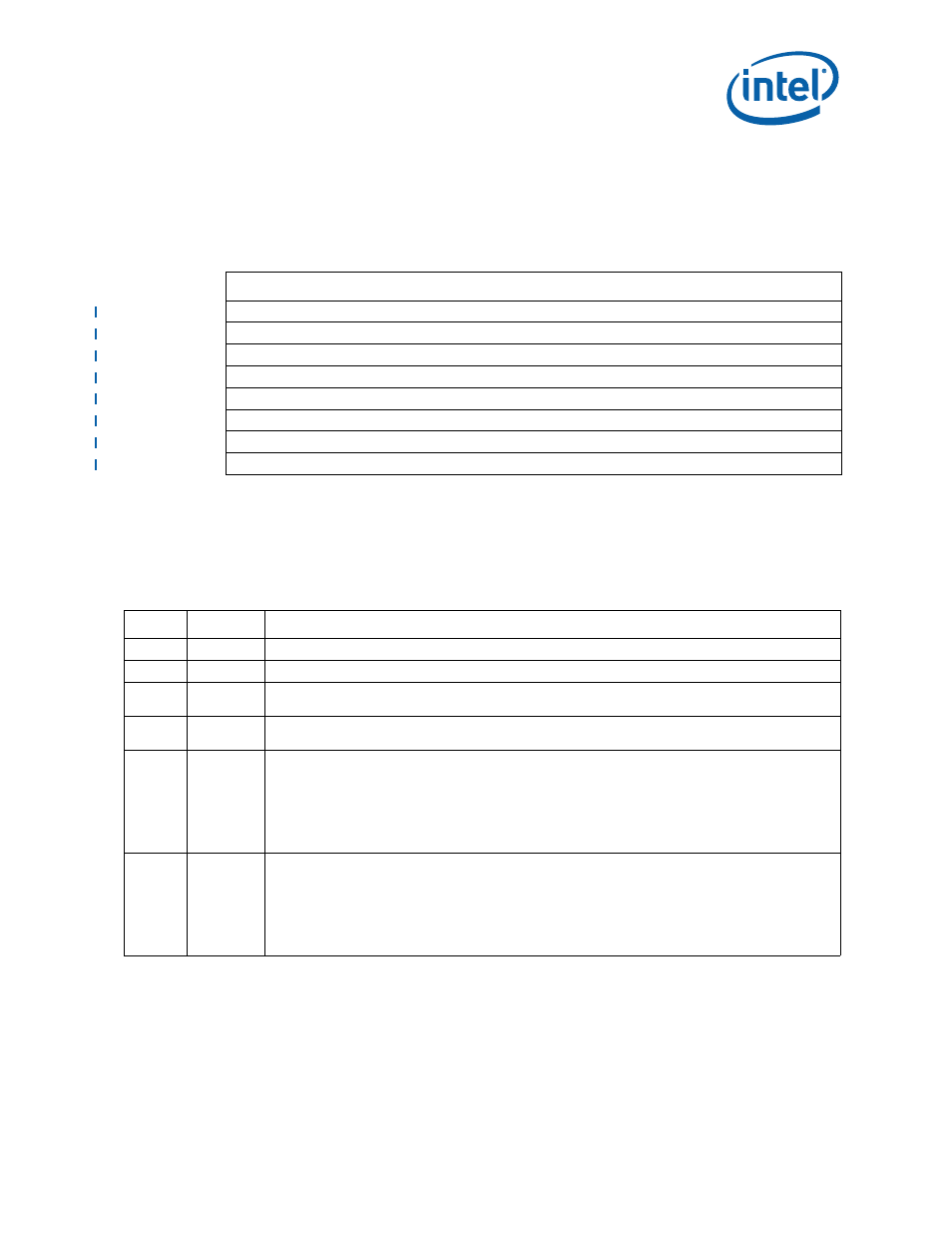

Table 433. SMBus Register Summary

Section, Register Name, Acronym, Page

Section 434, “SMBus Controller Command Register — SM_CMD” on page 655

Section 435, “SMBus Controller Byte Count Register — SM_BC” on page 656

Section 436, “SMBus Controller ADDR3 Register — SM_ADDR3” on page 656

Section 437, “SMBus Controller ADDR2 Register — SM_ADDR2” on page 656

Section 438, “SMBus Controller ADDR1 Register Number — SM_ADDR1” on page 657

Section 439, “SMBus Controller ADDR0 Register Number — SM_ADDR0” on page 657

Section 440, “SMBus Controller Data Register — SM_DATA” on page 658

Section 441, “SMBus Controller Status Register — SM_STS” on page 658

Table 434. SMBus Controller Command Register — SM_CMD

Bit

Reset

Description

07

0

Begin: The Begin bit when set indicates the first transaction of the read or write sequence.

06

0

End: The End bit when set indicates the last transaction of the read or write sequence.

05

0

Memory/Configure: Indicate whether memory or configuration space is being accesses in this SMBus

sequence. Value of ‘1’ indicates memory and a value of ‘0’ indicate configuration.

04

0

PEC Enable: Indicates that PEC is enabled when set. When set, each transaction in the sequence ends

with an extra CRC byte. 4138xx would check for CRC on writes and generate CRC on reads.

03:02

00

Internal Command:

00 — Read DWord

01 — Write Byte

10 — Write Word

11 — Write Dword

All access are naturally aligned to the access width. This field specifies the internal command to be

issued by the SMBus slave logic to the 4138xx

01:00

00

SMBus command:

00 — Byte

01 — Word

10 — Block

11 — Reserved

This field specifies the SMBus command to be issued on the SMBus. This field is used as an indication

of the length of transfer so that the slave knows when to expect the PEC packet (when enabled).