4 compactpci hot-swap, 1 pin interface, Table 7. compact pci hot-swap – Intel CONTROLLERS 413808 User Manual

Page 80: 7 compact pci hot-swap, Hs_sm

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

80

Order Number: 317805-001US

2.4

CompactPCI Hot-Swap

The 4138xx meets the standard requirements to be considered “Hot-Swap Silicon”

detailed in the Compact PCI Hot-Swap Specification, Revision 2.1. This includes a

dedicated pin interface and extended capability header.

Hot-Swap Control and Status Register is implemented via the Extended Capability

Pointer mechanism in the ATUs configuration space (

Hot-Swap Capability ID Register”

).

Provides Software Connection Control Resources for ENUM#, Hot-Swap Switch, blue

LED and Device Hiding.

Handle Switch de-bouncing is implemented.

See

Section 2.4.1.1, “Compact PCI Hot-Swap Mode Select”

for a description of

HS_SM#

and HS_FREQ[1:0] requirements.

2.4.1

Pin Interface

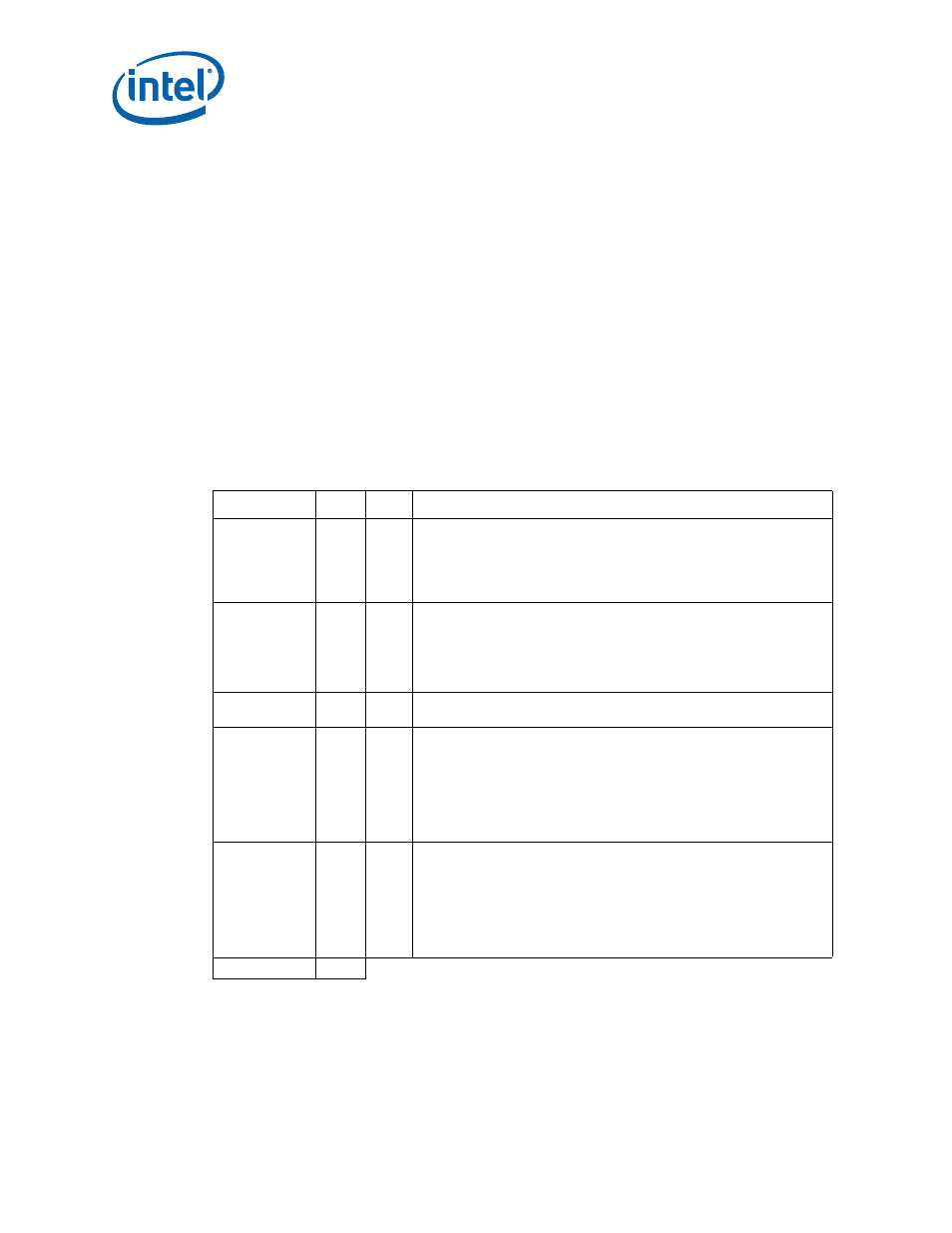

Table 7.

Compact PCI Hot-Swap

Signal

Width Type

Description

HS_ENUM#

1

Od-O

Compact PCI Hot-Swap Event:

Conditionally asserted to notify the system host that either a board has

been freshly inserted or is about to be extracted. This signal informs the

system host that the configuration of the system has changed. The system

host then performs any necessary maintenance such as installing or

quiesing a device driver.

HS_LSTAT

1

I

Compact PCI Hot-Swap Latch Status:

An input indicating the state of the ejector switch.

0 = Indicates the ejector switch is closed.

1 = Indicates the ejector switch is open.

When Compact PCI Hot-Swap is not supported, this signal must be tied

low.

HS_LED_OUT

1

O

LED Output:

4138xx outputs a logic one to illuminate the Hot-Swap LED.

HS_SM#

1

I

Hot-Swap Startup Mode (Strap):

This strap is sampled at the rising edge of P_RST# to indicate Hot-Swap

Mode.

When 1b and Configuration Retry Mode enabled (bit 2 of the PCSR),

indicates 4138xx retries all Configuration transactions.

When 0b and Configuration Retry Mode enabled (bit 2 of the PCSR),

indicates 4138xx does not claim Configuration transactions and the bus

mode is determined by the HS_FREQ[1:0] straps.

HS_FREQ[1:0]

2

I

This pins are reserved for determining Bus frequency and mode during a

PCI-X Hot-Swap event and are only valid when

HS_SM#

= 0. The bus

frequency and mode are described below:

11 => PCI Mode, 33 or 66 MHz. Use P_M66EN to determine frequency

10 => PCI-X Mode, 66 MHz

01 => PCI-X Mode, 100 MHz

00 => PCI-X Mode, 133 MHz

These pins are not used for non-Hot-Swap systems.

Total

6