3 inbound delayed write queue, Req64 – Intel CONTROLLERS 413808 User Manual

Page 85

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

85

Address Translation Unit (PCI-X)—Intel

®

413808 and 413812

2.6.1.3

Inbound Delayed Write Queue

The IDWQ is used specifically for inbound configuration write cycles to the ATU. I/O

Write transactions are not accepted by the ATU and result in a Master Abort.

The IDWQ contains both the address and data of a configuration write cycle. When

operating in the conventional PCI mode, the configuration writes are handled as

delayed writes. When operating in the PCI-X mode, the configuration writes are

handled as split writes. When the write cycle is initiated on the PCI bus, the address

and data are entered into the 8 byte queue, and forwarded to the internal bus. The

transaction is forwarded to the internal bus once transaction ordering has been

satisfied. The status of the transaction (normal completion) is maintained in the IDWQ

for return to the PCI master on the initiating bus. When operating in the PCI-X mode, a

write completion message is generated by the ATU to indicate the successful execution

of the configuration write transaction.

The IDWQ can only hold 32-bits of data and should never be accessed with

REQ64#

asserted per the PCI Local Bus Specification, Revision 2.3 which states that “only

memory transactions support 64-bit data transfers”. In addition, the cycle should

always return only 32-bits of data on the internal bus.

2.6.1.4

Inbound Transaction Queues Command Translation Summary

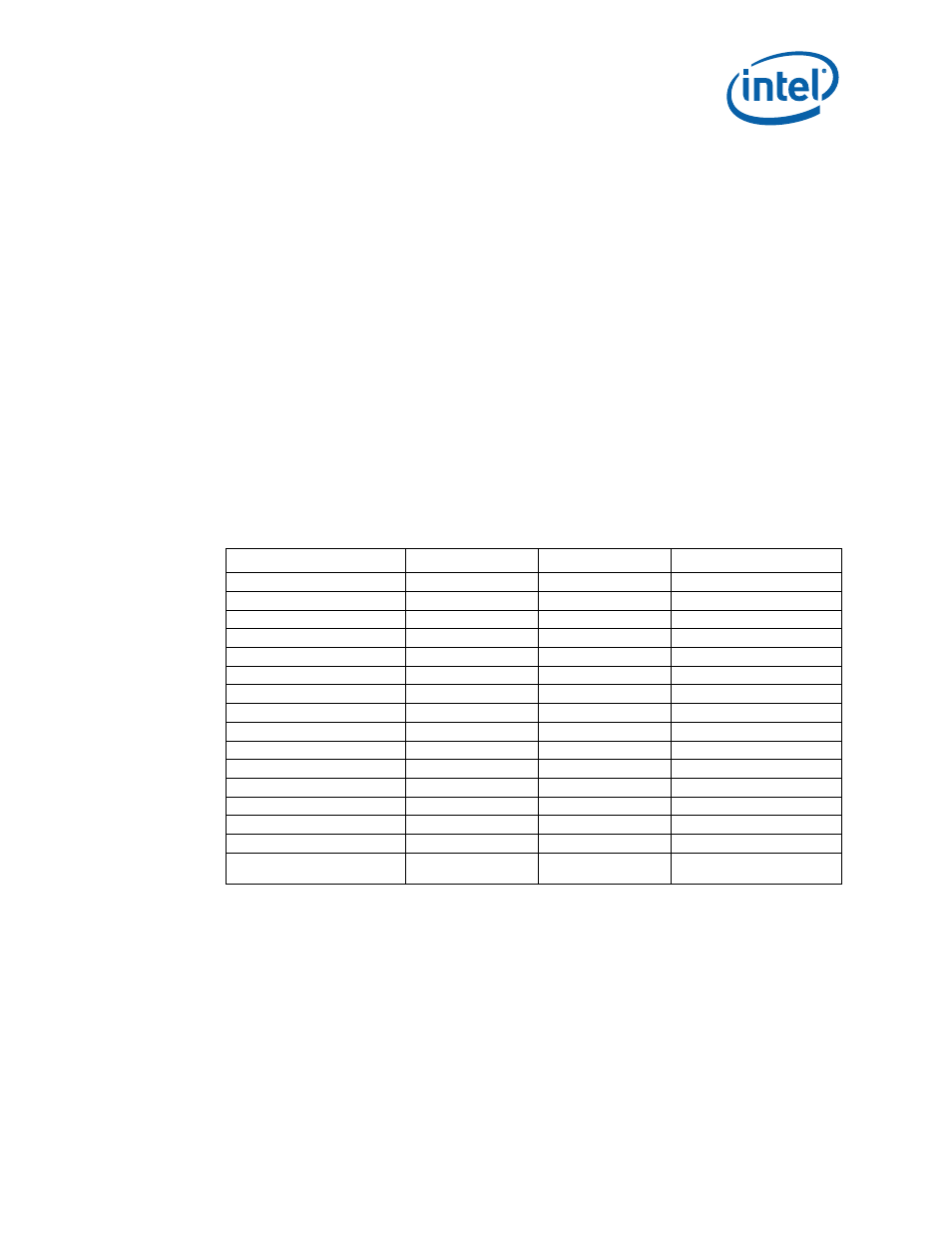

Table 11. PCI to Internal Bus Command Translation for All Inbound Transactions

PCI Command

Conventional Mode

PCI-X Mode

Internal Bus Command

Memory Write

a

a

Write

Memory Write and Invalidate

a

Write

Memory Write Block

a

Write

Alias to Memory Write Block

a

Write

Memory Read

a

Read

Memory Read Line

a

Read

Memory Read Multiple

a

Read

Memory Read Block

a

Read

Alias to Memory Read Block

a

Read

Memory Read DWORD

a

Read

Configuration Read

a

a

Read

Configuration Write

a

a

Write

Split Read Completion

a

Data Transfer

Split Write Completion

a

None

Split Completion Error Message

a

Data Transfer Abort

All Other Commands Not

Claimed by the ATU

a

a

N/A