8 messaging unit, Table 538. messaging unit offset, Table 539. messaging unit (sheet 1 of 2) – Intel CONTROLLERS 413808 User Manual

Page 806: 538 messaging unit offset, 539 messaging unit, Messaging unit

Intel

®

413808 and 413812—Peripheral Registers

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

806

Order Number: 317805-001US

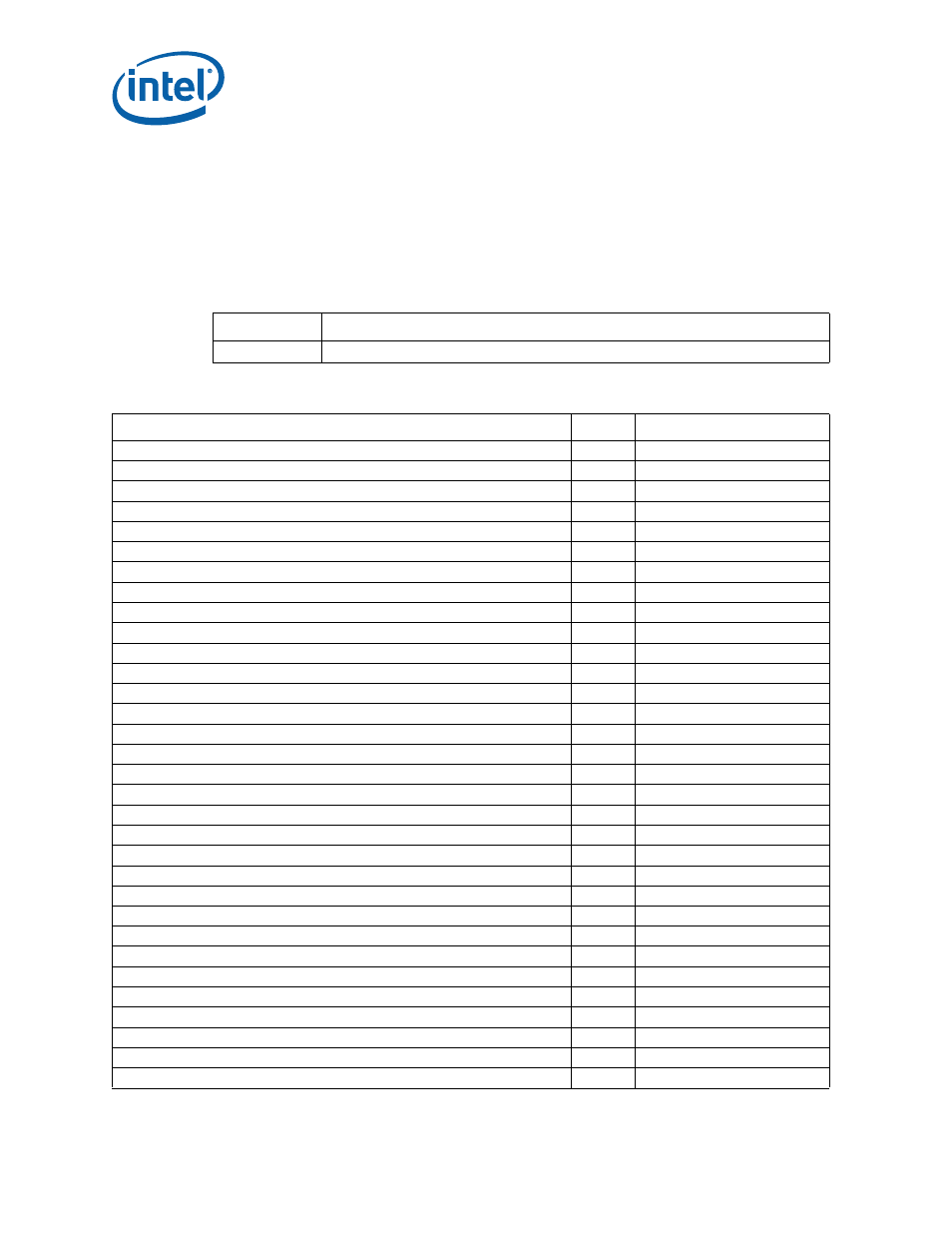

19.6.1.8 Messaging Unit

The Messaging Unit (MU) is allocated 8 KBytes of PMMR registers space that is located

which is relative to the PMMRBAR.

Use the following equation to calculate the actual register address:

Internal Bus Address = PMMRBAR + MU Base Address Offset + Register Offset.

Table 538. Messaging Unit Offset.

Unit

MU Base Address Offset (Relative to PMMRBAR)

Messaging Unit

+4000H

Table 539. Messaging Unit (Sheet 1 of 2)

Register Description (Name)

Bits

Internal Bus Address Offset

a

Reserved

x

+000H — +00C

Inbound Message Register — IMR0

32

+010H

Inbound Message Register — IMR1

32

+014H

Outbound Message Register — OMR0

32

+018H

Outbound Message Register — OMR1

32

+01CH

Inbound Doorbell Register — IDR

32

+020H

Inbound Interrupt Status Register — IISR

32

+024H

Inbound Interrupt Mask Register — IIMR

32

+028H

Outbound Doorbell Register — ODR

32

+02CH

Outbound Interrupt Status Register — OISR

32

+030H

Outbound Interrupt Mask Register — OIMR

32

+034H

Inbound Reset Control and Status Register — IRCSR

32

+038H

Outbound Reset Control and Status Register — ORCSR

32

+03CH

Reserved

x

+040H — +047H

MSI Inbound Message Register

32

+048H

Reserved

x

+04CH

MU Configuration Register — MUCR

32

+050H

Reserved

32

+054H

Reserved

32

+058H

Reserved

32

+05CH

Reserved

32

+060H

Reserved

32

+064H

Reserved

32

+068H

Reserved

32

+06CH

Reserved

32

+070H

Reserved

32

+074H

Reserved

32

+078H

Reserved

32

+07CH

Reserved

32

+080H

MU Base Address Register — MUBAR

32

+084H

MU Upper Base Address Register — MUUBAR

32

+088H

Reserved

x

+08CH — +0FFH