31 inbound atu limit register 1 - ialr1, Table 171. inbound atu limit register 1 - ialr1, 31inbound atu limit register 1 - ialr1 – Intel CONTROLLERS 413808 User Manual

Page 320: 171 inbound atu limit register 1 - ialr1, Intel, Bit default description

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

320

Order Number: 317805-001US

3.17.31 Inbound ATU Limit Register 1 - IALR1

Inbound address translation for memory window 1 occurs for transactions originated in

the PCI Express domain and targeting the 4138xx internal bus. The address translation

block converts PCI addresses to internal bus addresses.

The inbound translation base address for inbound window 1 is specified in

. When determining block size requirements — as described in

— the translation limit register provides the block size requirements for

the base address register. The remaining registers used for performing address

translation are discussed in

.

The 4138xx value register’s programmed value must be naturally aligned with the base

address register’s programmed value. The limit register is used as a mask; thus, the

lower address bits programmed into the 4138xx value register are invalid. Refer to the

PCI Local Bus Specification, Revision 2.3 for additional information on programming

base address registers.

Bits 31 to 12 within the IALR1 have a direct effect on the IABAR1 register, bits 31 to 12,

with a one to one correspondence. A value of 0 in a bit within the IALR1 makes the

corresponding bit within the IABAR1 a read only bit which always returns 0. A value of

1 in a bit within the IALR1 makes the corresponding bit within the IABAR1 read/write

from PCI. Note that a consequence of this programming scheme is that unless a valid

value exists within the IALR1, all writes to the IABAR1 has no effect since a value of all

zeros within the IALR1 makes the IABAR1 a read only register.

Note:

Bit 0 can be used to disable claiming of Memory Cycles that hit Inbound Memory

Window 1 even though the host processor has allocated memory of the size requested

by IABAR1/IALR1[31:12].

.

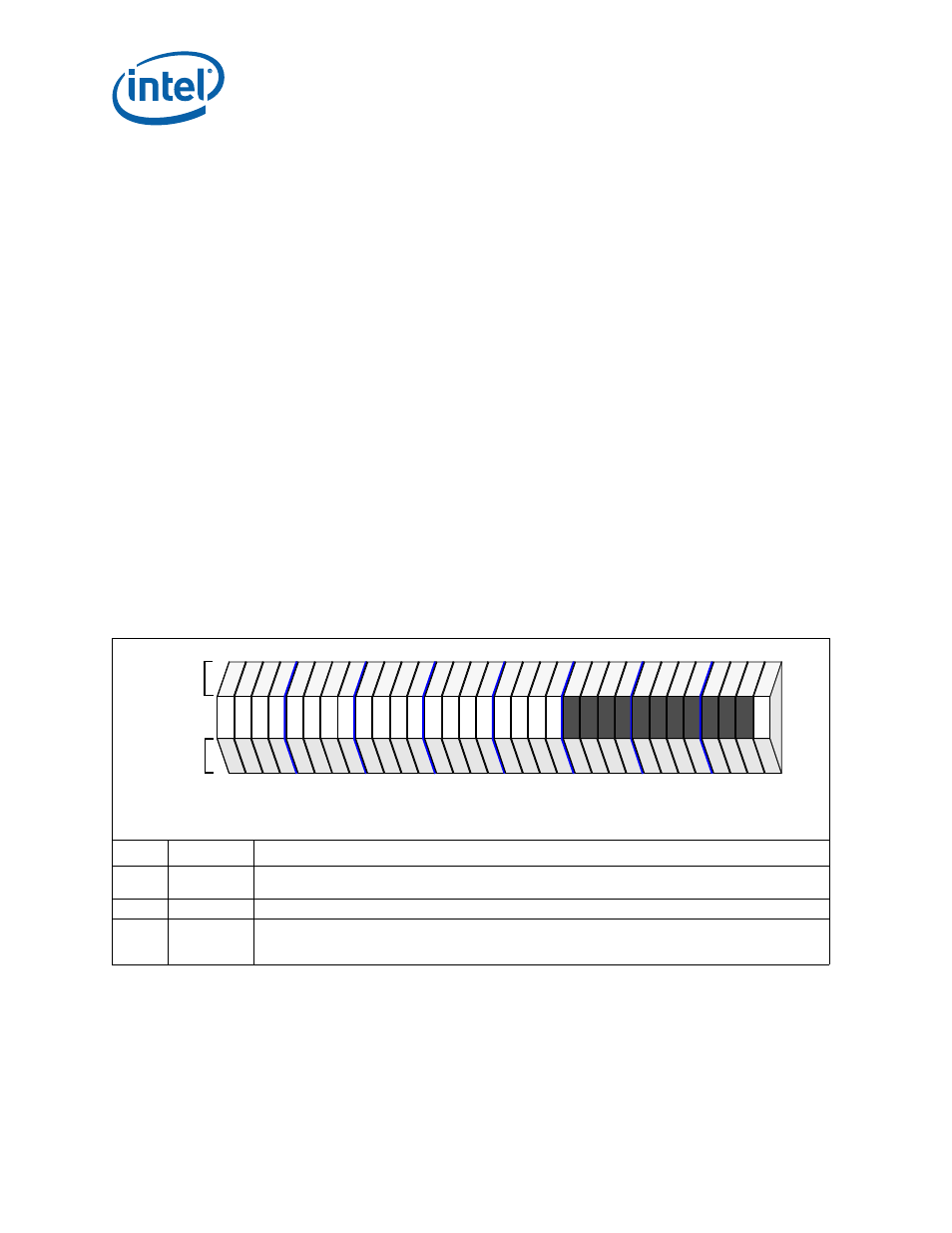

Table 171. Inbound ATU Limit Register 1 - IALR1

Bit

Default

Description

31:12

00000H

Inbound Translation Limit 1 - This readback value determines the memory block size required for the

ATUs memory window 1.

11:01

000H

Reserved

00

0

2

Memory Window 1 Claim Disable -- When clear, Inbound Memory Window 1 claims PCI Memory Cycles

Normally. When set, memory transactions targeting Inbound Memory Window 0 is terminated as an

Unsupported Request (UR).

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+04CH