2 sda arbitration, Figure 98. arbitration procedure of two masters, 98 arbitration procedure of two masters – Intel CONTROLLERS 413808 User Manual

Page 701

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

701

I

2

C Bus Interface Units—Intel

®

413808 and 413812

14.3.3.2

SDA Arbitration

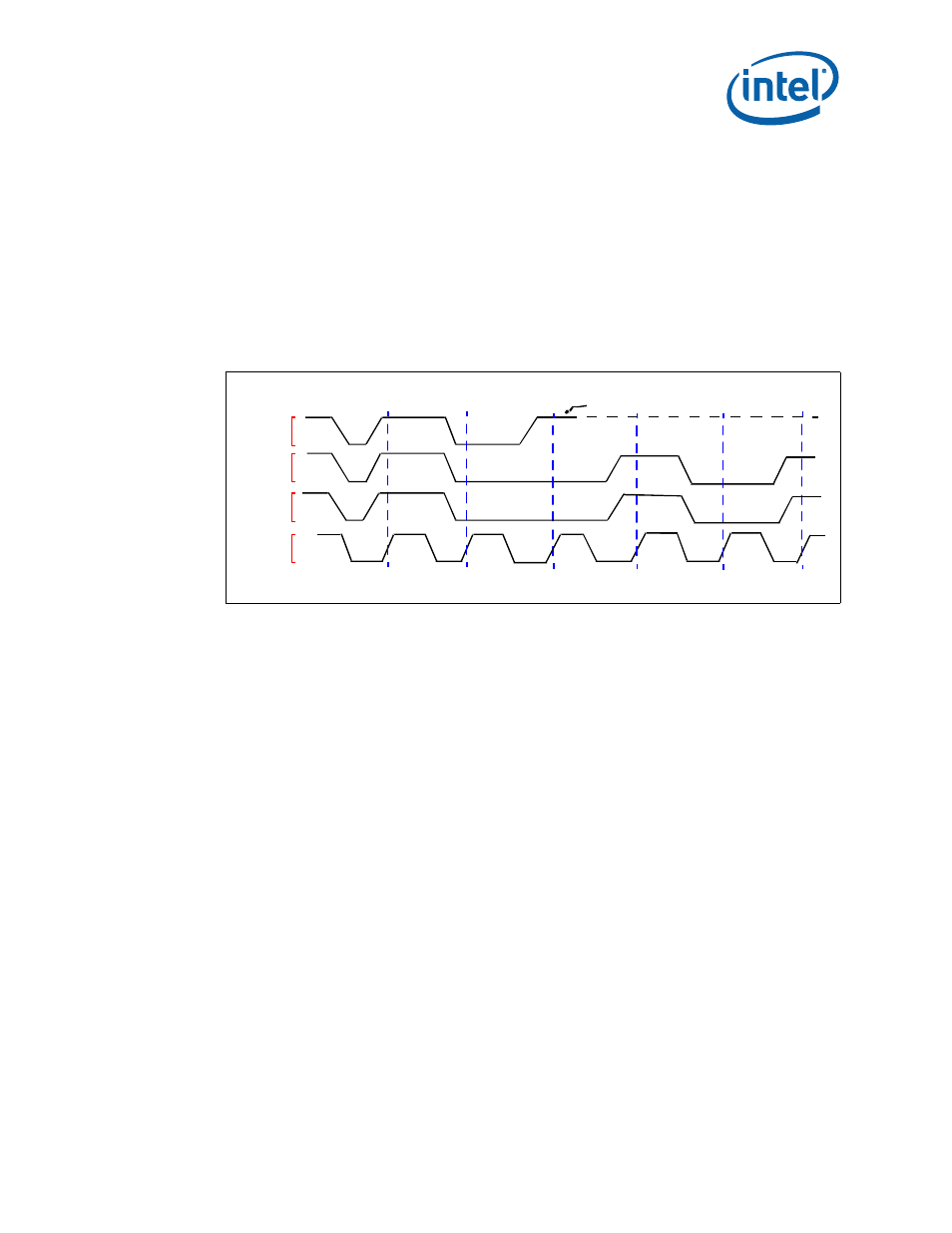

Arbitration on the

SDA

line can continue for a long period, starting with address and

R/W# bits and continuing with data bits.

shows the arbitration procedure for

two masters (more than two may be involved depending on how many masters are

connected to the bus). When the address and R/W# are the same, arbitration moves to

the data. Due to the wired-AND nature of the I

2

C bus, no data is lost when both (or all)

masters are outputting the same bus states. When address, R/W#, or data is different,

the master that output the first low data bit loses arbitration and shuts its data drivers

off. When the I

2

C unit loses arbitration, it shuts off the

SDA

or

SCL

drivers for

remainder of byte transfer, sets arbitration loss detected ISR bit, then returns to idle

(Slave-Receive) mode.

When the I

2

C unit loses arbitration during transmission of the seven address bits and

the 4138xx is not being addressed as a slave device, the I

2

C unit re-sends the address

when the I

2

C bus becomes free. This is possible because the IDBR and ICR registers

are not overwritten when arbitration is lost.

When the arbitration loss is to due to another bus master addressing the 4138xx as a

slave device, the I

2

C unit switches to slave-receive mode and the original data in the

I

2

C data buffer register is overwritten. Software is responsible for clearing the start and

re-initiating the master transaction at a later time.

Note:

Software must not allow the I

2

C unit to write to its own slave address. This can cause

the I

2

C bus to enter an indeterminate state.

Boundary conditions exist for arbitration when an arbitration process is in progress and

a repeated START or STOP condition is transmitted on the I

2

C bus. To prevent errors,

the I

2

C unit, acting as a master, provides for the following sequences:

• No arbitration takes place between a repeated START condition and a data bit

• No arbitration takes place between a data bit and a STOP condition

• No arbitration takes place between a repeated START condition and a STOP

condition

These situations arise only when different masters write the same data to the same

target slave simultaneously and arbitration is not resolved after the first data byte

transfer.

Note:

Typically, software is responsible for ensuring arbitration is lost soon after the

transaction begins. For example, the protocol might insist that all masters transmit

their I

2

C address as the first data byte of any transaction ensuring arbitration is ended.

A restart is then sent to begin a valid data transfer (slave can discard master address).

Figure 98. Arbitration Procedure of Two Masters

SDA

SCL

Data 1

Data 2

Transmitter 1 Leaves Arbitration Data 1 SDA

B6288-01