Figure 101. a complete data transfer, 99 master-receiver read from slave-transmitter, Slave-receiver704 – Intel CONTROLLERS 413808 User Manual

Page 704: 101 a complete data transfer, When the 4138xx needs to read data, the i, For a complete data transfer, Intel, C bus interface units

Intel

®

413808 and 413812—I

2

C Bus Interface Units

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

704

Order Number: 317805-001US

When the 4138xx needs to read data, the I

2

C unit transitions from slave-receive mode

to master-transmit mode to transmit the start address and immediately following the

ACK pulse transitions to master-receive mode to wait for the reception of the read data

). It is also possible to have multiple transactions

during an I

2

C operation such as transitioning from master-receive to master-transmit

through a repeated start or Data Chaining (see

shows the

wave forms of

SDA

and

SCL

for a complete data transfer.

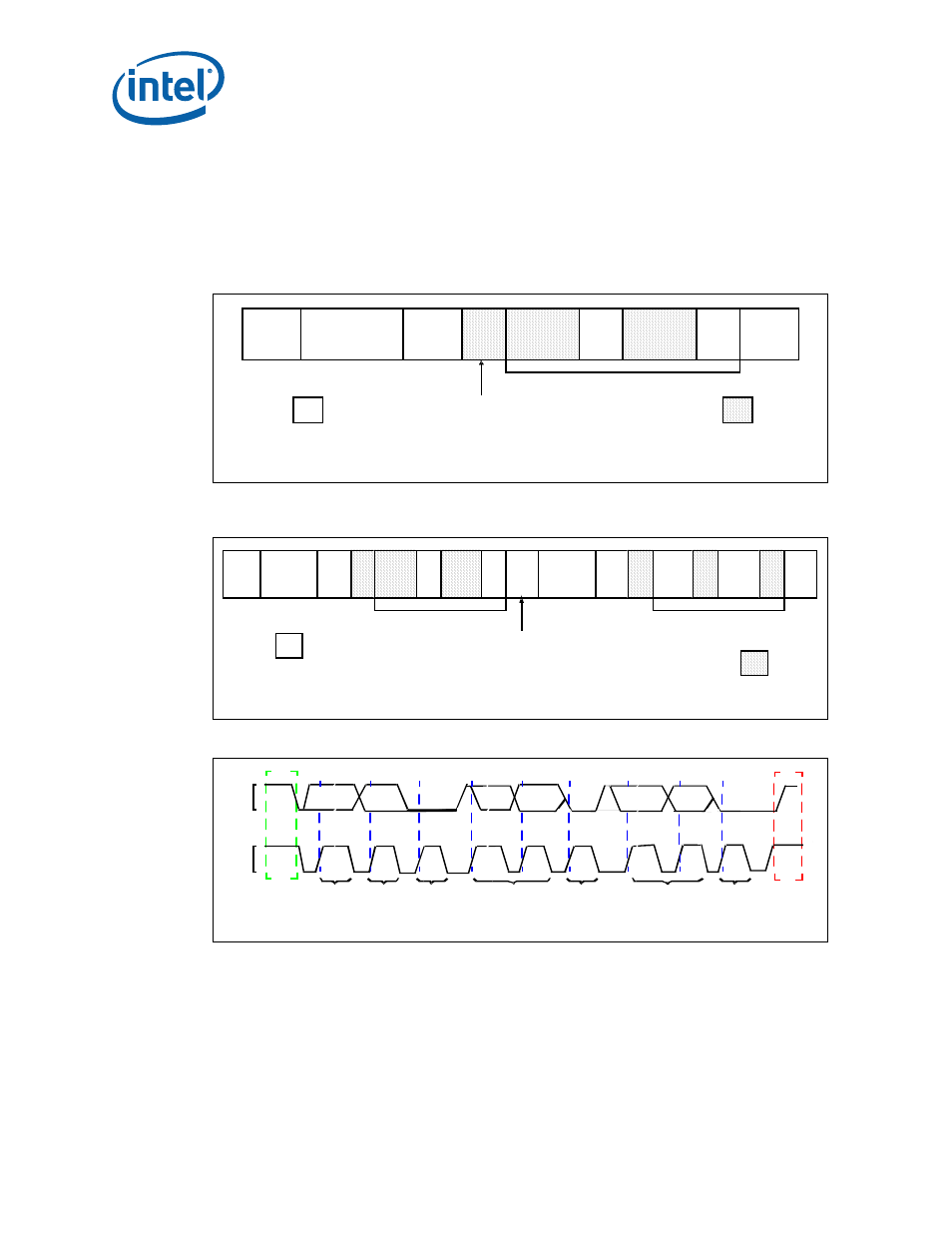

Figure 99. Master-Receiver Read from Slave-Transmitter

Figure 100. Master-Receiver Read from Slave-Transmitter / Repeated Start

/Master-Transmitter Write to Slave-Receiver

Figure 101. A Complete Data Transfer

Master to Slave

Slave to Master

START

Slave

Address

R/W#

1

ACK

Data

Byte

ACK

Data

Byte

STOP

N Bytes + ACK

ACK

Default

Slave-Receive

Mode

First Byte

Read

B6289-01

Start Slave

R

/W

#

1

Data

Byte

Data

Byte

N Bytes + ACK

Read

Sr

Slave

R

/W

#

0

A

C

K Data

Byte

Data

Byte

S

TO

P

N Bytes + ACK

Write

Address

Address

Master to Slave

Slave to Master

Repeated

Start

Data Chaining

A

C

K

A

C

K

A

C

K

A

C

K

A

C

K

B6290-01

SDA

SCL

Start

Condition

Address R/W# ACK

Data

ACK

Data

1-7

8

9

8

9

8

9

1-7

1-7

ACK

Stop

Condition

~

~

~

~

~

~

~

~

~

~

~

~

~

~

~

~

~

~

B6291-01