1 gpio output enable register - gpoe, Table 478. gpio output enable register - gpoe, 1 gpio output enable register — gpoe – Intel CONTROLLERS 413808 User Manual

Page 725: 478 gpio output enable register — gpoe, Section 15.2.1, “gpio, Gpio[15:0, P_rst, Table 478. gpio output enable register — gpoe, General purpose i/o unit—intel, Bit default description

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

725

General Purpose I/O Unit—Intel

®

413808 and 413812

15.2.1

GPIO Output Enable Register — GPOE

The GPIO Output Enable Register, on a per pin basis, enables the output value

contained in the GPIO Output Data Register, onto the appropriate pin. The GPIO Output

Enable Register is initialized to FFFFH such that all of

GPIO[15:0]

are inputs. In order

to enable a particular GPIO pin to operate as an output following the deassertion of

P_RST#

, the user needs to write a 0 into the appropriate GPOE bit.

Table 478. GPIO Output Enable Register — GPOE

Bit

Default

Description

31:16

0000H

Reserved.

15

1

2

GPIO15 Output Enable — When clear, bit[15] of the GPIO Output Data Register is enabled onto the

GPIO[15]

pin.

14

1

2

GPIO14 Output Enable — When clear, bit[14] of the GPIO Output Data Register is enabled onto the

GPIO[14]

pin.

13

1

2

GPIO13 Output Enable — When clear, bit[13] of the GPIO Output Data Register is enabled onto the

GPIO[13]

pin.

12

1

2

GPIO12 Output Enable — When clear, bit[12] of the GPIO Output Data Register is enabled onto the

GPIO[12]

pin.

11

1

2

GPIO11 Output Enable — When clear, bit[11] of the GPIO Output Data Register is enabled onto the

GPIO[11]

pin.

10

1

2

GPIO10 Output Enable — When clear, bit[10] of the GPIO Output Data Register is enabled onto the

GPIO[10]

pin.

09

1

2

GPIO9 Output Enable — When clear, bit[9] of the GPIO Output Data Register is enabled onto the

GPIO[9]

pin.

08

1

2

GPIO8 Output Enable — When clear, bit[8] of the GPIO Output Data Register is enabled onto the

GPIO[8]

pin.

07

1

2

GPIO7 Output Enable — When clear, bit[7] of the GPIO Output Data Register is enabled onto the

GPIO[7]

pin.

06

1

2

GPIO6 Output Enable — When clear, bit[6] of the GPIO Output Data Register is enabled onto the

GPIO[6]

pin.

05

1

2

GPIO5 Output Enable — When clear, bit[5] of the GPIO Output Data Register is enabled onto the

GPIO[5]

pin.

04

1

2

GPIO4 Output Enable — When clear, bit[4] of the GPIO Output Data Register is enabled onto the

GPIO[4]

pin.

03

1

2

GPIO3 Output Enable — When clear, bit[3] of the GPIO Output Data Register is enabled onto the

GPIO[3]

pin.

02

1

2

GPIO2 Output Enable — When clear, bit[2] of the GPIO Output Data Register is enabled onto the

GPIO[2]

pin.

01

1

2

GPIO1 Output Enable — When clear, bit[1] of the GPIO Output Data Register is enabled onto the

GPIO[1]

pin.

00

1

2

GPIO0 Output Enable — When clear, bit[0] of the GPIO Output Data Register is enabled onto the

GPIO[0]

pin.

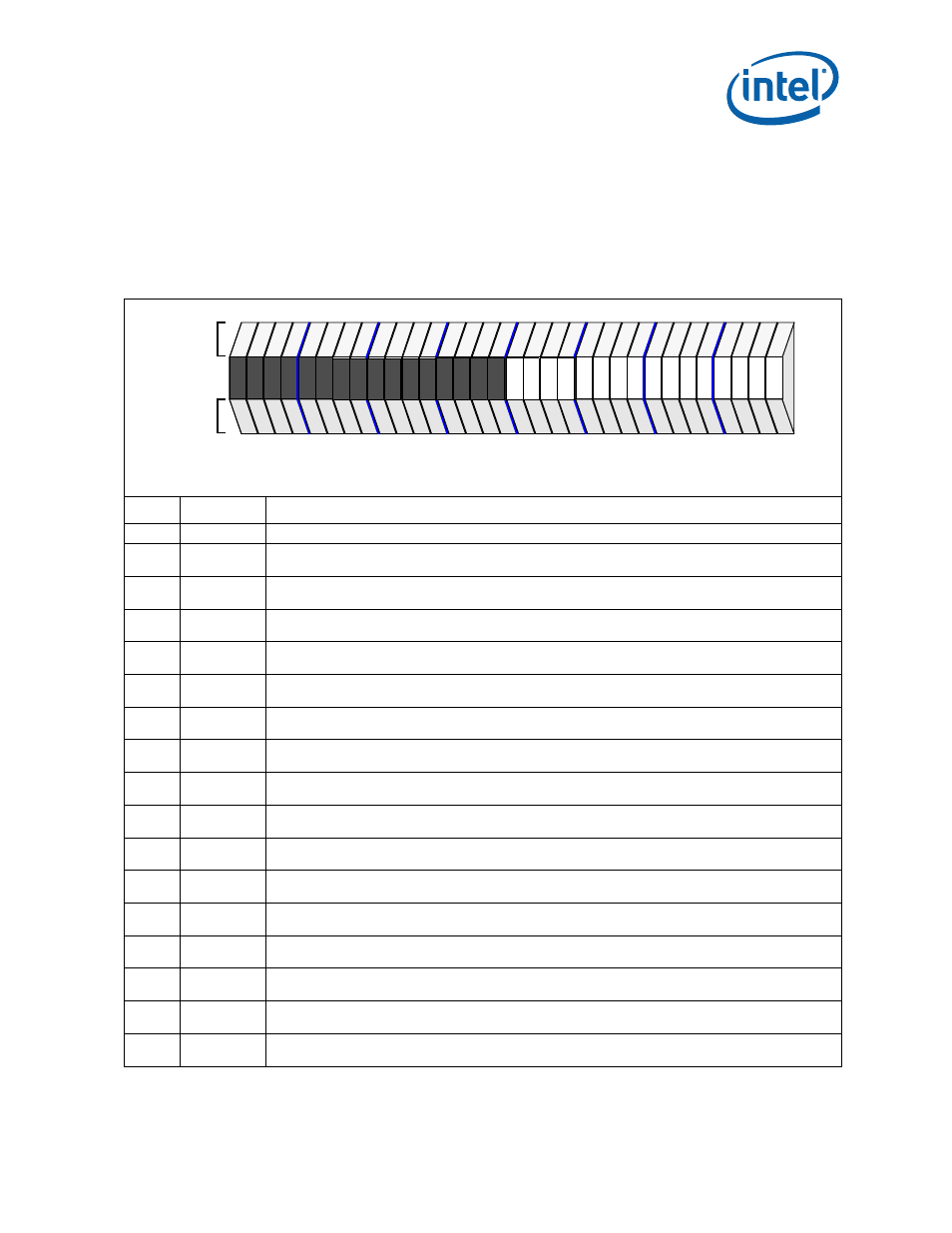

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Intel XScale

®

processor Local Bus Address

offset

+2480H