1 uart x receive buffer register, 2 uart x transmit holding register, 447 uart x receive buffer register - (uxrbr) – Intel CONTROLLERS 413808 User Manual

Page 670: 448 uart x transmit holding register - (uxthr), Intel, Bit default description, Unit # 01 intel xscale

Intel

®

413808 and 413812—UARTs

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

670

Order Number: 317805-001US

13.4.1

UART x Receive Buffer Register

In non-FIFO mode, this register holds the character(s) received by the UART Receive

Shift register. When it receives fewer than eight bits, the bits are right-justified and the

leading bits are zeroed. Reading the register empties the register and resets the data

ready (DR) bit in the Line Status register to 0. Other (error) bits in the Line Status

register are not cleared. In FIFO mode, this register latches the value of the data

byte(s) at the bottom of the FIFO.

When the UART is in eight-bit Peripheral Bus mode, the 24 most significant bits must be

ignored and not used. Reading these bits returns unpredictable results.

.

13.4.2

UART x Transmit Holding Register

This register holds the next data byte(s) to be transmitted. When the Transmit Shift

register becomes empty, the contents of the Transmit Holding register are loaded into

the Shift register and the Transmit Data Request (TDRQ) bit in the Line Status register

is set to one (see

Table 451, “Interrupt Identification Register Decode” on page 673

).

In FIFO mode, writing to THR puts data to the top of the FIFO. The data at the bottom

of the FIFO is loaded to the Shift register when it is empty. In eight-bit Peripheral

mode, the 24 most significant bits are ignored and is not transmitted.

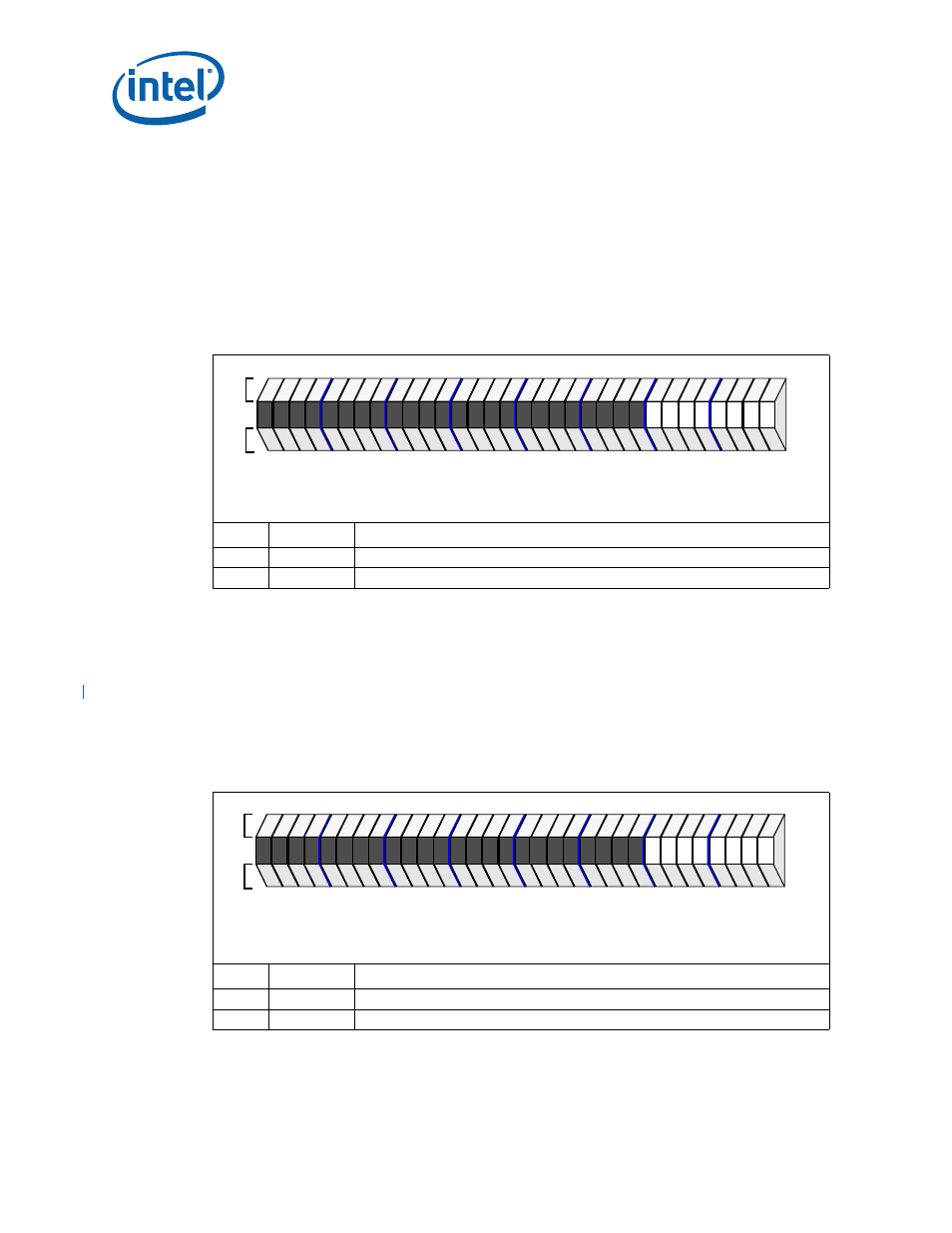

Table 447. UART x Receive Buffer Register - (UxRBR)

Bit

Default

Description

31:8

00h

Reserved

7:0

00h

Data Byte

P

C

I

IO

P

A

tt

ri

b

u

te

s

A

tt

ri

b

u

te

s

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

Unit #

01

Intel XScale

®

Core internal bus address

+2300H (DLAB=0)

+2340H (DLAB=0)

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Table 448. UART x Transmit Holding Register - (UxTHR)

Bit

Default

Description

31:8

00h

Reserved

7:0

00h

Data Byte

PC

I

IO

P

A

tt

ri

b

u

te

s

A

tt

ri

b

u

te

s

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

wo

na

wo

na

wo

na

wo

na

wo

na

wo

na

wo

na

wo

na

Unit #

01

Intel XScale

®

Core internal bus address

+2300H (DLAB=0)

+2340H (DLAB=0)

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

WO = Write Only

NA = Not Accessible