1 programmer model, 1 active interrupt source control and status – Intel CONTROLLERS 413808 User Manual

Page 573

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

573

Interrupt Controller Unit—Intel

®

413808 and 413812

10.5.1

Programmer Model

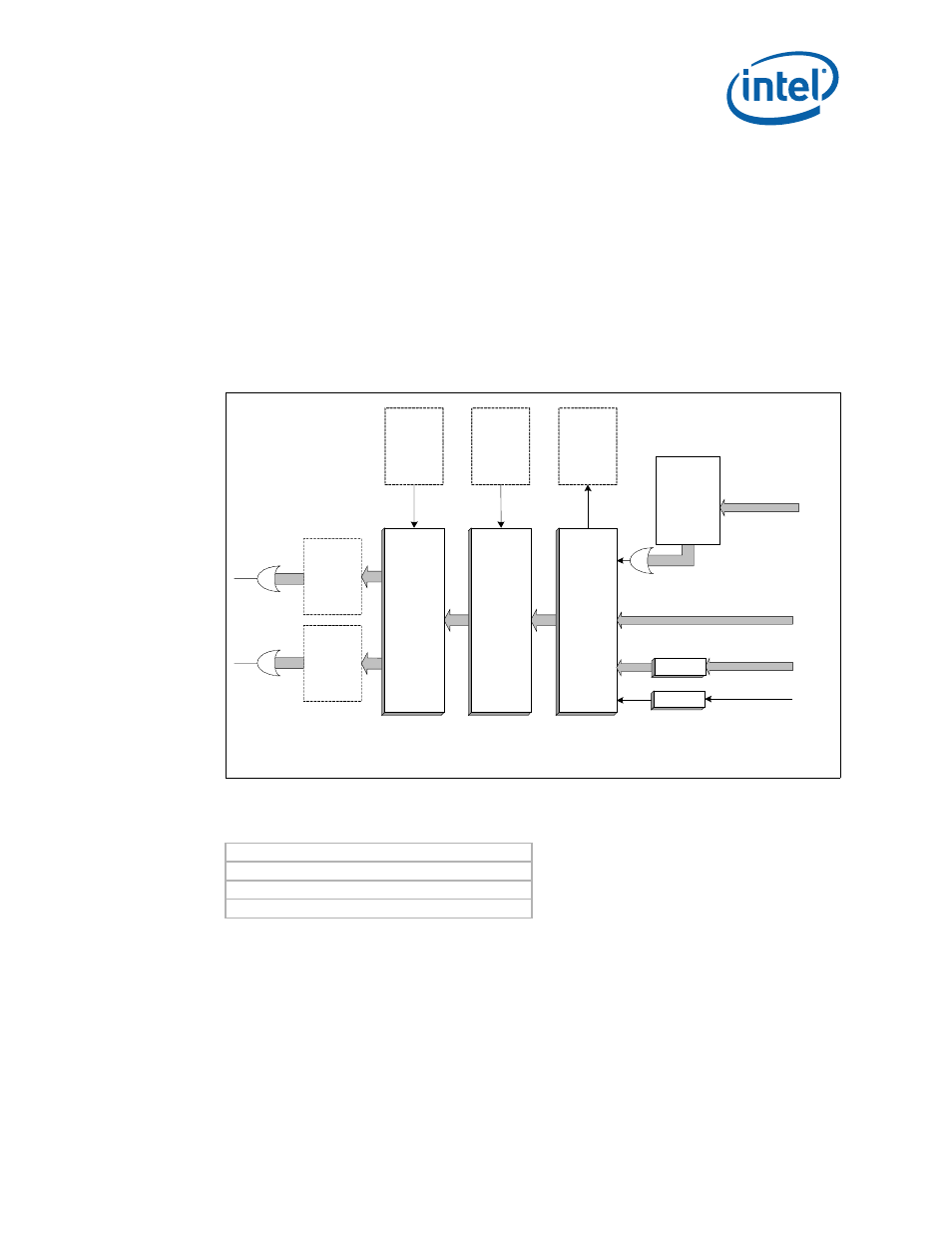

Software has access to 15 registers in the ICU. These registers control, masking,

prioritization, and vector generation for all interrupt sources.

10.5.1.1 Active Interrupt Source Control and Status

The INTCTL[3:0] are used to enable or disable (mask) individual interrupts. As

mentioned, masking of all interrupts may still be accomplished via the CPSR register in

the core. INTSTR[3:0] are used to direct internal interrupts to either FIQ or IRQ.

IINTSRC[3:0] and FINTSRC[3:0] are read-only registers that record all currently active

and unmasked interrupt sources; the architecture for the interrupt source registers and

FIQ/IRQ generation is illustrated in

.

10.5.1.2 Prioritization and Vector Generation for Active Interrupt Sources

IPR[7:0] registers reserve two bits for each source to assign one of four priority levels.

When interrupt vector generation is enabled and there are multiple requests pending

either in the FINTSRC[3:0] or the IINTSRC[3:0] registers, the prioritization selects a

highest priority active source for each source register.

Note:

When multiple interrupts at the same priority level are pending for either FIQ or IRQ,

the highest priority active source is selected according to a fixed priority based on bit

location. Highest order bit is first.

Figure 68. Interrupt Controller Block Diagram (Active Interrupt Source Registers)

FIQ

Interrupt

Source

Register

[3:0]

Internal

FIQ

Internal

IRQ

IRQ

Interrupt

Source

Register

[3:0]

Interrupt

Pending

Interrupt

Masking

INTSTR

Interrupt

Steering

Register

[3:0]

INTCTL

Interrupt

Control

Register

[3:0]

INTPND

Interrupt

Pending

Register

[3:0]

Internal

Interrupt

Steering

Synch

Synch

Mask

Control

Steer

Control

Peripheral and Intel Xscale® processor

internal interrupts

XINT15:0#

HPI#

Notes:

Other brands and names may be claimed as the property of others.

IPIPNDR

Inter-

processor

Interrupt

Pending

Register

Inter-processor

Interrupts

Intel XScale® microarchitecture is ARM* architecture compliant.

B6272-01

00

2 —

High Priority

01

2 —

Medium/High Priority

10

2 —

Medium/Low Priority

11

2 —

Low Priority