4 pmon data register 0-7 - pmon_data[0:7, Table 495. pmon data register 7-0 - pmon_data[7:0, Pmon – Intel CONTROLLERS 413808 User Manual

Page 756: Intel, Bit default description, Counter x value

Intel

®

413808 and 413812—PMON Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

756

Order Number: 317805-001US

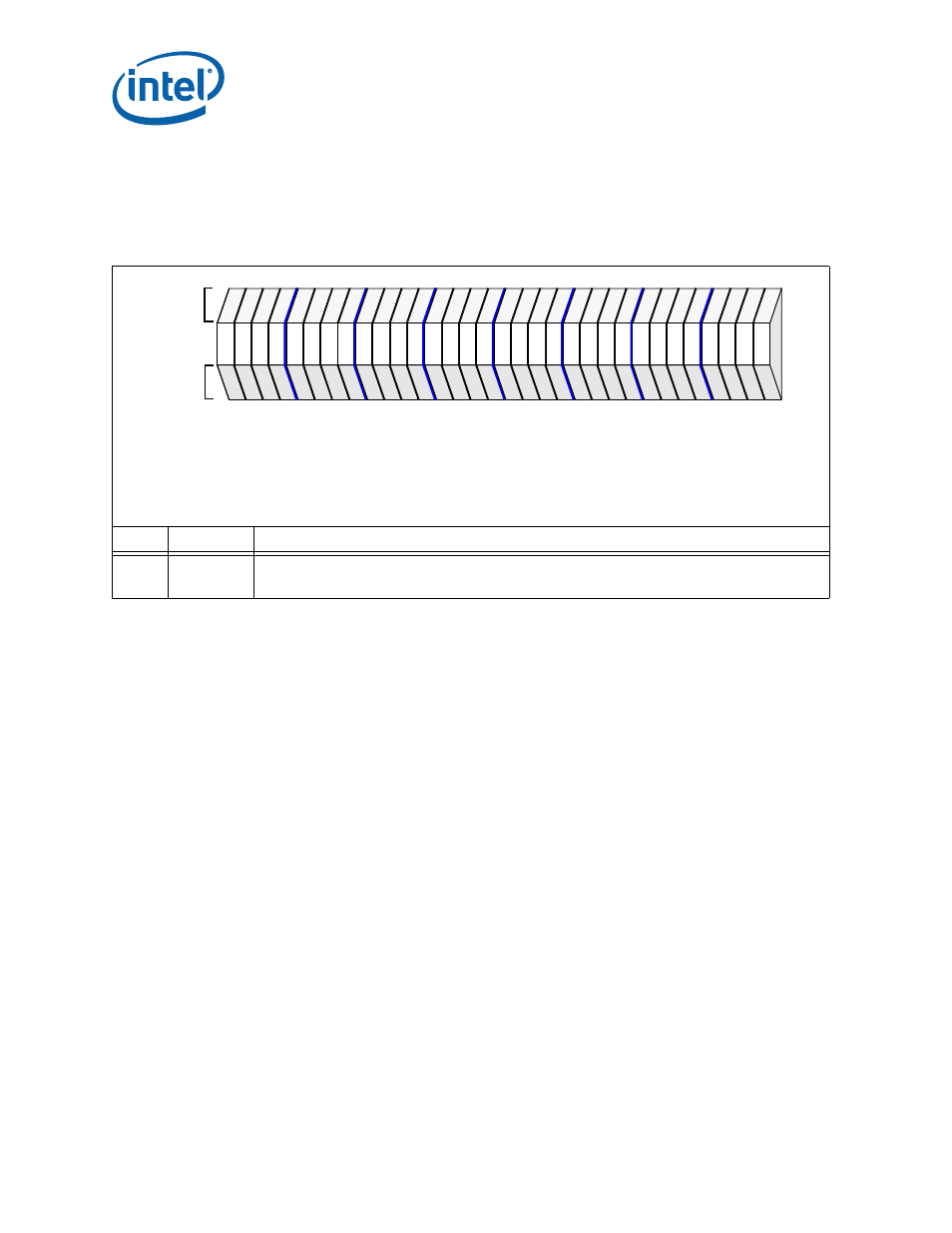

16.5.6.4 PMON Data Register 0-7 - PMON_DATA[0:7]

This 32-bit register allows for reading of the sampled value from

PMON

event counter

X and contains the threshold value that is compared to the value in the event counter

when a threshold condition (non-0 condition code) is in effect.

Table 495. PMON DATA Register 7-0 - PMON_DATA[7:0]

Bit

Default

Description

31:0

0000 0000h

Counter X Value:

Contains either duration (number of clock ticks) or occurrences contained in

PMON

event counter n at time of sampling. The register is programmed to contain the threshold value that is

compared to the value in the event counter when non-0 condition codes have been selected.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

PMON

_DATA0

PMON

_DATA1

PMON

_DATA2

PMON

_DATA3

PMON

_DATA4

PMON

_DATA5

PMON

_DATA6

PMON

_DATA7

+00Ch

+01Ch

+02Ch

+03Ch

+04Ch

+05Ch

+06Ch

+07Ch