Intel, Serr, Bit default description – Intel CONTROLLERS 413808 User Manual

Page 184

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

184

Order Number: 317805-001US

06

0

2

ATU

SERR#

Asserted Interrupt Mask - Controls the setting of bit 10 of the ATUISR and generation of the

ATU Error interrupt when

SERR#

is asserted on the PCI interface resulting in bit 14 of the ATUSR being

set.

0 = Not Masked

1 = Masked

Note:

This bit is specific to the ATU asserting

SERR#

and not detecting

SERR#

from another master.

05

0

2

ATU PCI Master Abort Interrupt Mask - Controls the setting of bit 3 of the ATUISR and generation of the

ATU Error interrupt when a master abort error resulting in bit 13 of the ATUSR being set.

0 = Not Masked

1 = Masked

04

0

2

ATU PCI Target Abort (Master) Interrupt Mask- Controls the setting of bit 12 of the ATUISR and ATU Error

generation of the interrupt when a target abort error resulting in bit 12 of the ATUSR being set

0 = Not Masked

1 = Masked

03

0

2

ATU PCI Target Abort (Target) Interrupt Mask- Controls the setting of bit 1 of the ATUISR and generation

of the ATU Error interrupt when a target abort error resulting in bit 11 of the ATUSR being set.

0 = Not Masked

1 = Masked

02

0

2

ATU PCI Master Parity Error Interrupt Mask - Controls the setting of bit 0 of the ATUISR and generation of

the ATU Error interrupt when a parity error resulting in bit 8 of the ATUSR being set.

0 = Not Masked

1 = Masked

01

0

2

ATU Inbound Error

SERR#

Enable - Controls when ATU asserts (when enabled through the ATUCMD)

SERR#

on the PCI interface in response to a master abort on the internal bus during an inbound write

transaction.

0 =

SERR#

Not Asserted due to error

1 =

SERR#

Asserted due to error

00

0

2

ATU ECC Target Abort Enable - Controls the ATU response on the PCI interface to a target abort (ECC

error) from the memory controller on the internal bus. In conventional mode, this action only occurs

during an inbound read transaction where the data phase that was target aborted on the internal bus is

actually requested from the inbound read queue.

0 = Disconnect with data (the data being up to 64 bits of 1’s)

1 = Target Abort

Note:

In PCI-X Mode, The ATU initiates a Split Completion Error Message (with message class=2h -

completer error and message index=81h - 4138xx internal bus target abort) on the PCI bus,

independent of the setting of this bit.

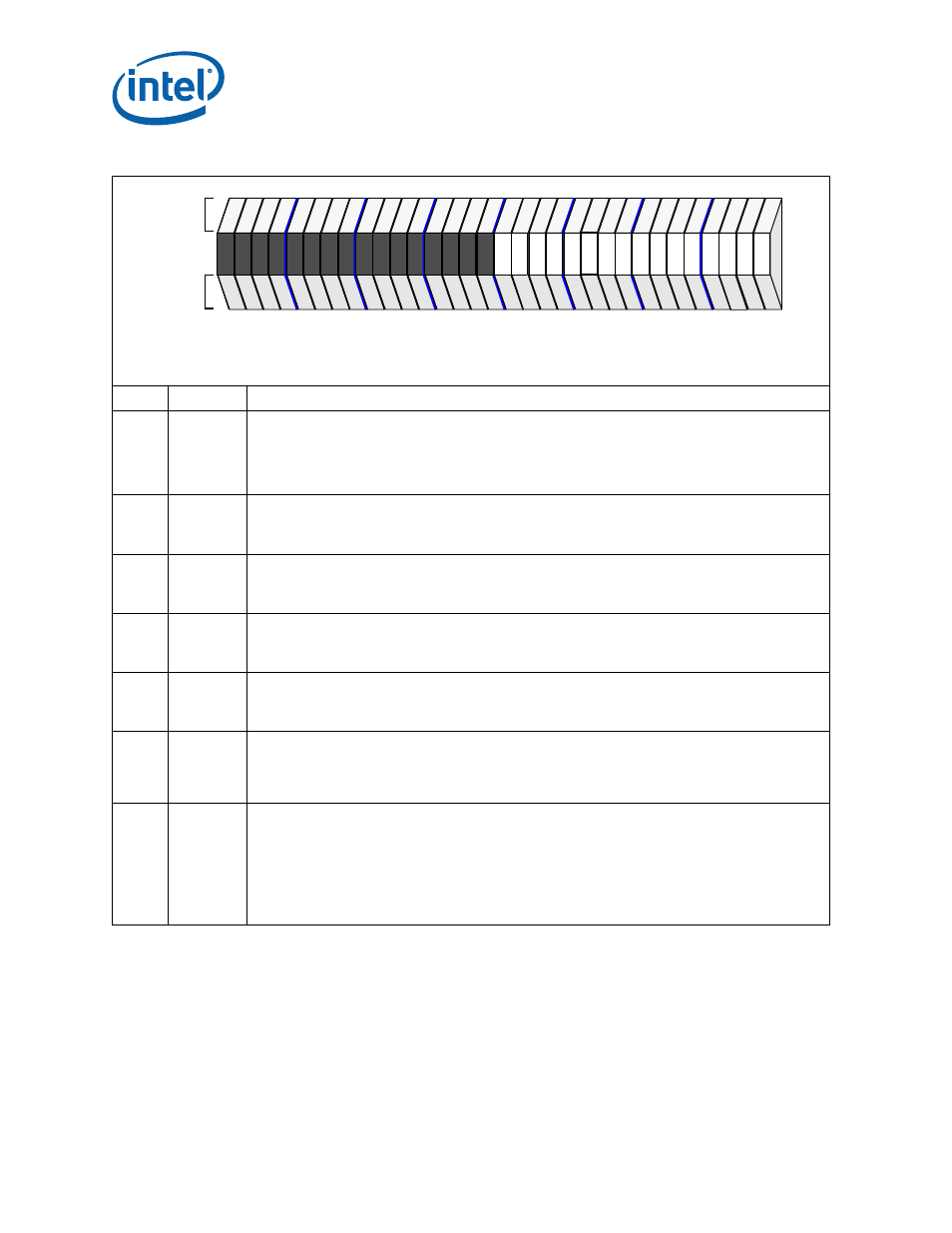

Table 70. ATU Interrupt Mask Register - ATUIMR (Sheet 2 of 2)

Bit

Default

Description

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

rv

rw

rw

rw

rv

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

+07CH