13 interrupt steering register 0 - intstr0, 13interrupt steering register 0 — intstr0, 395 interrupt steering register 0 — intstr0 – Intel CONTROLLERS 413808 User Manual

Page 598: 13 interrupt steering register 0 — intstr0

Intel

®

413808 and 413812—Interrupt Controller Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

598

Order Number: 317805-001US

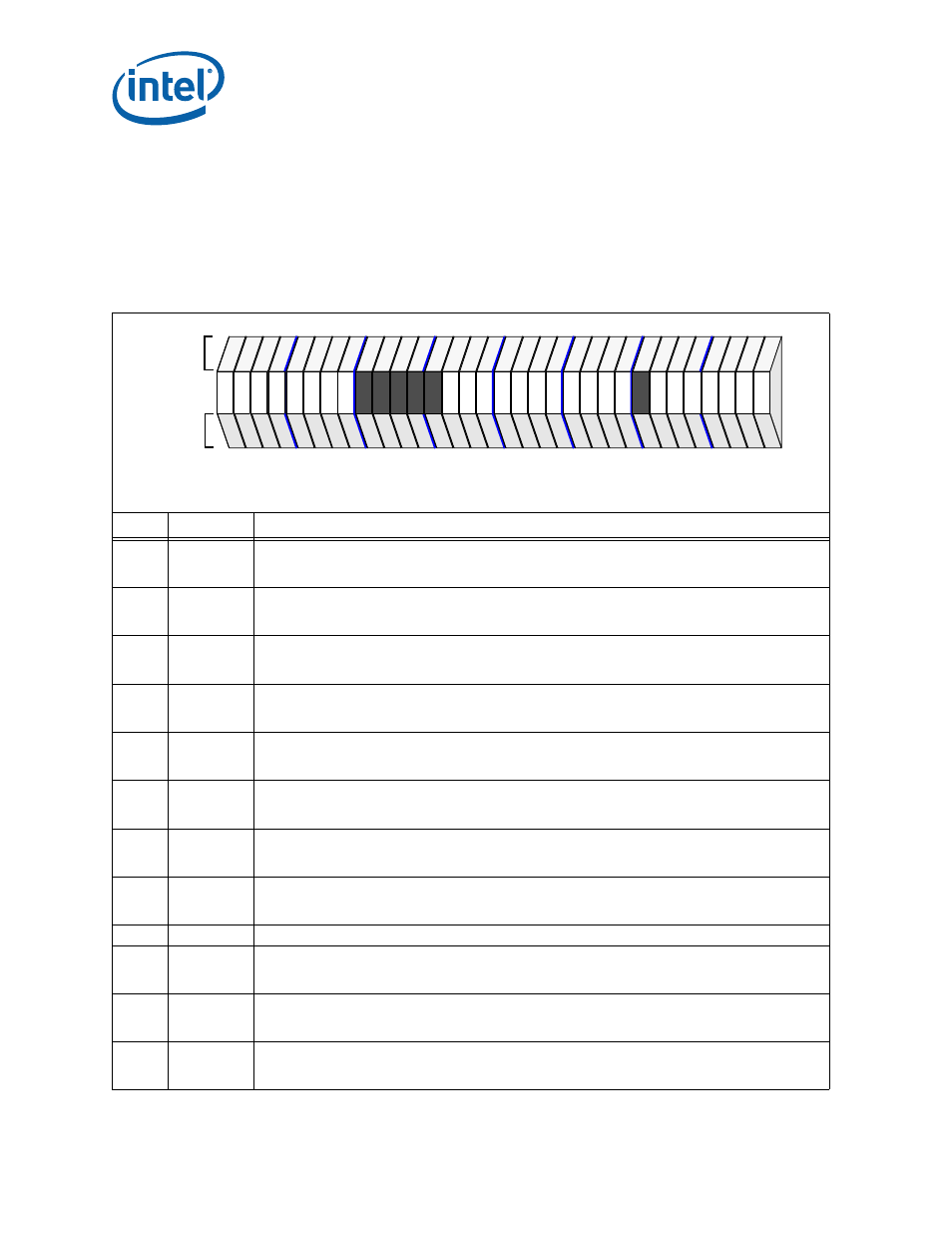

10.7.13 Interrupt Steering Register 0 — INTSTR0

The Interrupt Steering Register 0 allows system designers to direct any of 32 internal

or external interrupt sources to either one of the two internal interrupt exceptions, FIQ

and IRQ.

When an interrupt is enabled with the INTCTL0 register, this register steers the

interrupt to an internal interrupt exception.

Table 395. Interrupt Steering Register 0 — INTSTR0 (Sheet 1 of 2)

Bit

Default

Description

31

0

2

XINT7#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

30

0

2

XINT6#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

29

0

2

XINT5#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

28

0

2

XINT4#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

27

0

2

XINT3#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

26

0

2

XINT2#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

25

0

2

XINT1#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

24

0

2

XINT0#

Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

23:19

0

2

Reserved.

18

0

2

Intel XScale

®

Processor Cache Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

17

0

2

Intel XScale

®

Processor PMU Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

16

0

2

Peripheral Performance Monitor Interrupt Steering

0 = Interrupt Directed to Internal IRQ

1 = Interrupt Directed to Internal FIQ

Memory

Coprocessor

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Intel XScale

®

processor Coprocessor

address

CP6, Page 5, Register 0