18 irq interrupt source register 1 - iintsrc1, 18irq interrupt source register 1 — iintsrc1, 400 irq interrupt source register 1 — iintsrc1 – Intel CONTROLLERS 413808 User Manual

Page 607: 18 irq interrupt source register 1 — iintsrc1

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

607

Interrupt Controller Unit—Intel

®

413808 and 413812

10.7.18 IRQ Interrupt Source Register 1 — IINTSRC1

The IRQ Interrupt Source register is a 32-bit Coprocessor 6 control register used to

specify which of 32 interrupts that are steered to the internal IRQ exception are

unmasked by the INTCTL1 register and active. The INTSTR1 control register is used to

steer individual interrupts to the IRQ exception.

The IINTSRC1 register may be used by an Interrupt Service Routine (ISR) to determine

quickly the source of an IRQ interrupt.

Table 400. IRQ Interrupt Source Register 1 — IINTSRC1 (Sheet 1 of 2)

Bit

Default

Description

31

0

2

Reserved.

30

0

2

Messaging Unit Error Interrupt

0 = Not Interrupting or Not steered to internal IRQ exception or masked by INTCTL1

1 = Interrupting and steered to internal IRQ exception and unmasked by INTCTL1

29:28

0

2

Reserved.

27

0

2

Reserved.

26

0

2

Reserved.

25

0

2

Reserved.

24

0

2

Memory Controller Unit Error Interrupt — when set, an error condition exists within the MCU. The bit

indicates one of the following conditions:

• A single-bit correctable or uncorrectable ECC error.

• A multi-bit correctable or uncorrectable ECC error.

0 = Not Interrupting or Not steered to internal IRQ exception or masked by INTCTL1

1 = Interrupting and steered to internal IRQ exception and unmasked by INTCTL1

23

0

2

ATU Error Interrupt

0 = Not Interrupting or Not steered to internal IRQ exception or masked by INTCTL1

1 = Interrupting and steered to internal IRQ exception and unmasked by INTCTL1

22

0

2

ATU Configuration Register Write Interrupt

0 = Not Interrupting or Not steered to internal IRQ exception or masked by INTCTL1

1 = Interrupting and steered to internal IRQ exception and unmasked by INTCTL1

21

0

2

Peripheral Bus Interface Unit Error Interrupt

0 = Not Interrupting or Not steered to internal IRQ exception or masked by INTCTL1

1 = Interrupting and steered to internal IRQ exception and unmasked by INTCTL1

20

0

2

UART 1 Interrupt

0 = Not Interrupting or Not steered to internal IRQ exception or masked by INTCTL1

1 = Interrupting and steered to internal IRQ exception and unmasked by INTCTL1

19

0

2

UART 0 Interrupt

0 = Not Interrupting or Not steered to internal IRQ exception or masked by INTCTL1

1 = Interrupting and steered to internal IRQ exception and unmasked by INTCTL1

18:08

0000H

Reserved.

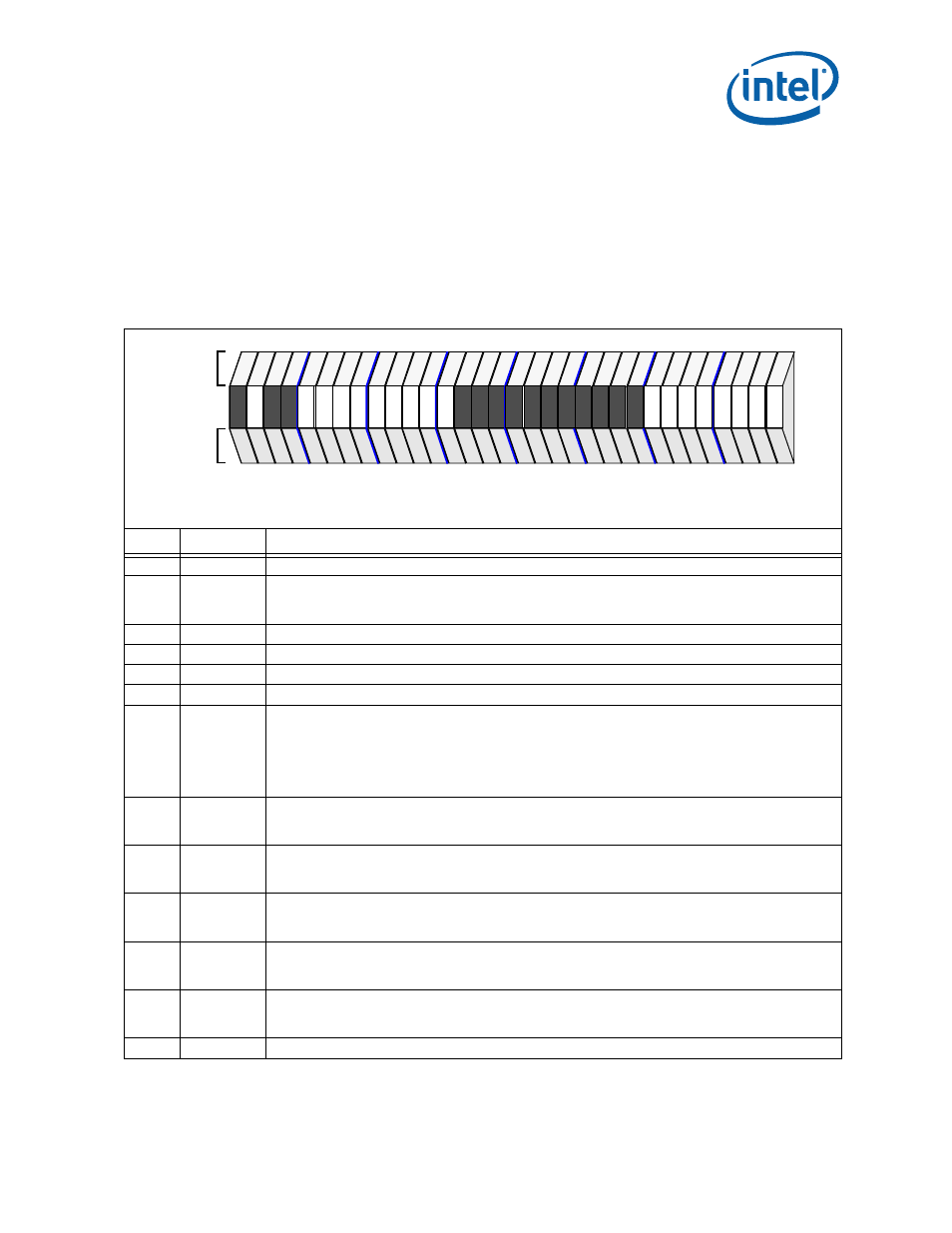

Memory

Coprocessor

Attributes

Attributes

28

24

20

16

12

8

4

0

31

ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro ro

na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Intel XScale

®

processor Coprocessor address

CP6, Page 6, Register 1