Table 508. hs_freq encoding, 3 end point mode (pcix_ep# = 0 and hs_sm# = 1), Table 509. pci-x initialization pattern1 – Intel CONTROLLERS 413808 User Manual

Page 766: 508 hs_freq encoding, 509 pci-x initialization pattern, Hs_sm, Pcix_ep, Hs_freq[1:0, P_m66en, Table 509. pci-x initialization patter n

Intel

®

413808 and 413812—Clocking and Reset

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

766

Order Number: 317805-001US

17.1.1.2.2 cPCI Hot-Swap Mode (PCIX_EP# = ‘0’ and HS_SM# = ‘0’)

When operating in a Compact PCI Hot-Swap environment (

HS_SM#

=0,

PCIX_EP#

=0), the

HS_FREQ[1:0]

and

P_M66EN

pins are used to determine PCI

Bus operating frequency and set default value in ATUX PCSR[19:16]. Inputs are

sampled at trailing edge of reset and used to set dividers on region 2 PLL.

17.1.1.2.3 End Point Mode (PCIX_EP# = 0 and HS_SM# = 1)

When operating in end point mode, the setting of PCSR[19:16] is determined by the

initialization pattern sampled off the PCI bus.

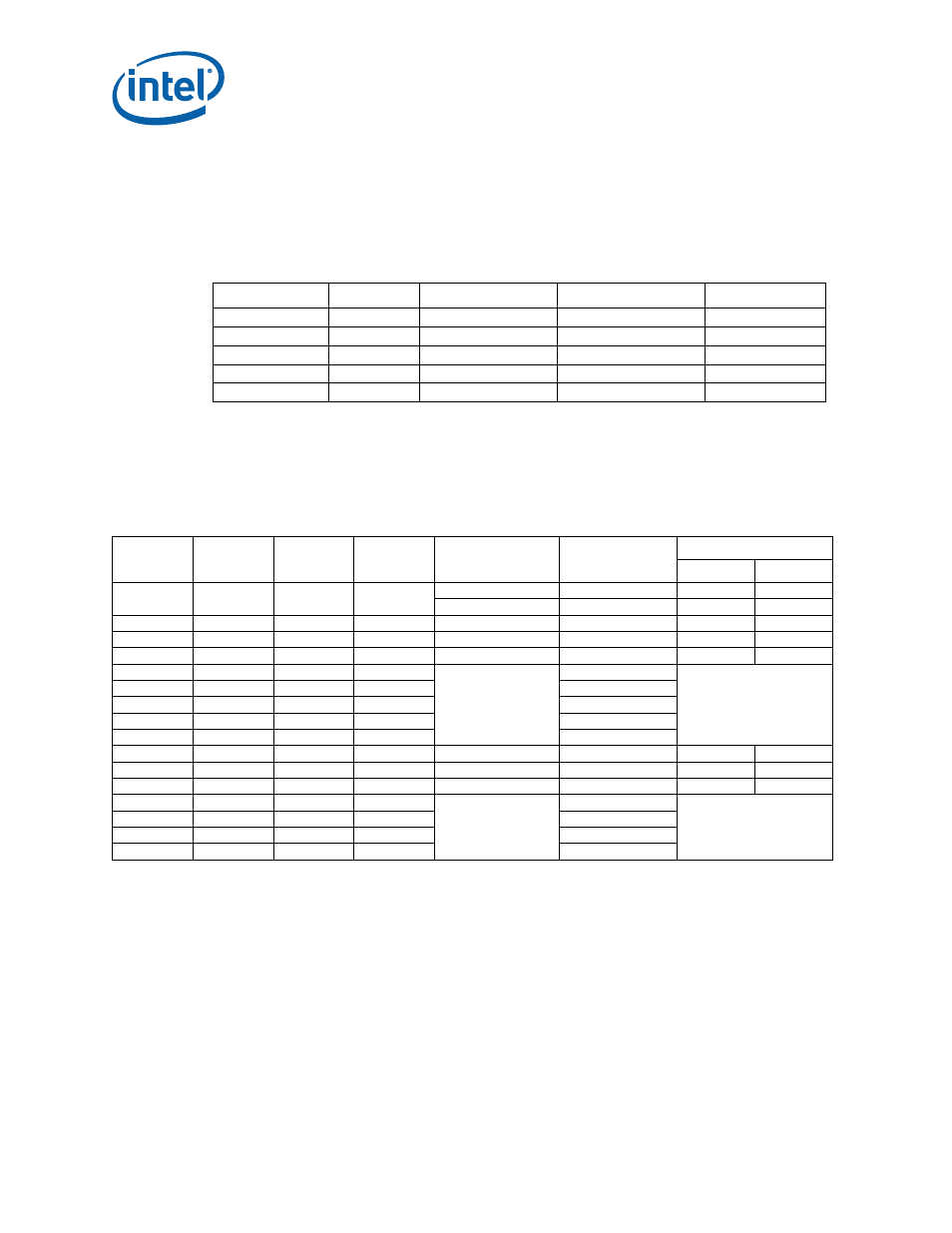

Table 508. HS_FREQ Encoding

a

a. Hot-Swap is not supported in PCI-X Mode 2.

HS_FREQ[1:0]

P_M66EN

Operating Mode

Bus Frequency

PCSR[19:16]

11

0

PCI

33 MHz

1111

11

1

PCI

66 MHz

1111

10

–

PCI-X (Mode 1)

66 MHz

1110

01

–

PCI-X (Mode 1)

100 MHz

1101

00

–

PCI-X (Mode 1)

133 MHz

1100

Table 509. PCI-X Initialization Pattern

PERR#

DEVSEL#

STOP#

TRDY#

ATUX

PCSR[19:16]

Mode

Clock Frequency (MHz)

Minimum Maximum

Deasserted Deasserted Deasserted Deasserted

1111

PCI 33

16

33

1111

PCI 66

33

66

Deasserted Deasserted Deasserted

Asserted

1110

PCI-X 66 Mode 1

50

66

Deasserted Deasserted

Asserted

Deasserted

1101

PCI-X100 Mode 1

66

100

Deasserted Deasserted

Asserted

Asserted

1100

PCI-X 133 Mode 1

100

133

Deasserted

Asserted

Deasserted Deasserted

Reserved

PCI-X Mode 1

Reserved

Deasserted

Asserted

Deasserted

Asserted

PCI-X Mode 1

Deasserted

Asserted

Asserted

Deasserted

PCI-X Mode 1

Deasserted

Asserted

Asserted

Asserted

PCI-X Mode 1

Asserted

Deasserted Deasserted Deasserted

PCI-X (Mode 2)

Asserted

Deasserted Deasserted

Asserted

0110

PCI-X 66 (Mode 2)

50

66

Asserted

Deasserted

Asserted

Deasserted

0101

PCI-X 100 (Mode 2)

66

100

Asserted

Deasserted

Asserted

Asserted

0100

PCI-X 133 (Mode 2)

100

133

Asserted

Asserted

Deasserted Deasserted

Reserved

PCI-X

Reserved

Asserted

Asserted

Deasserted

Asserted

PCI-X

Asserted

Asserted

Asserted

Deasserted

PCI-X

Asserted

Asserted

Asserted

Asserted

PCI-X

1.

81348 supports neither PCI-X 533 Mode nor ECC in Mode 1.