Sram dma unit (sdma)—intel, Bit default description, Reserved – Intel CONTROLLERS 413808 User Manual

Page 457: Intel

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

457

SRAM DMA Unit (SDMA)—Intel

®

413808 and 413812

5.4.14

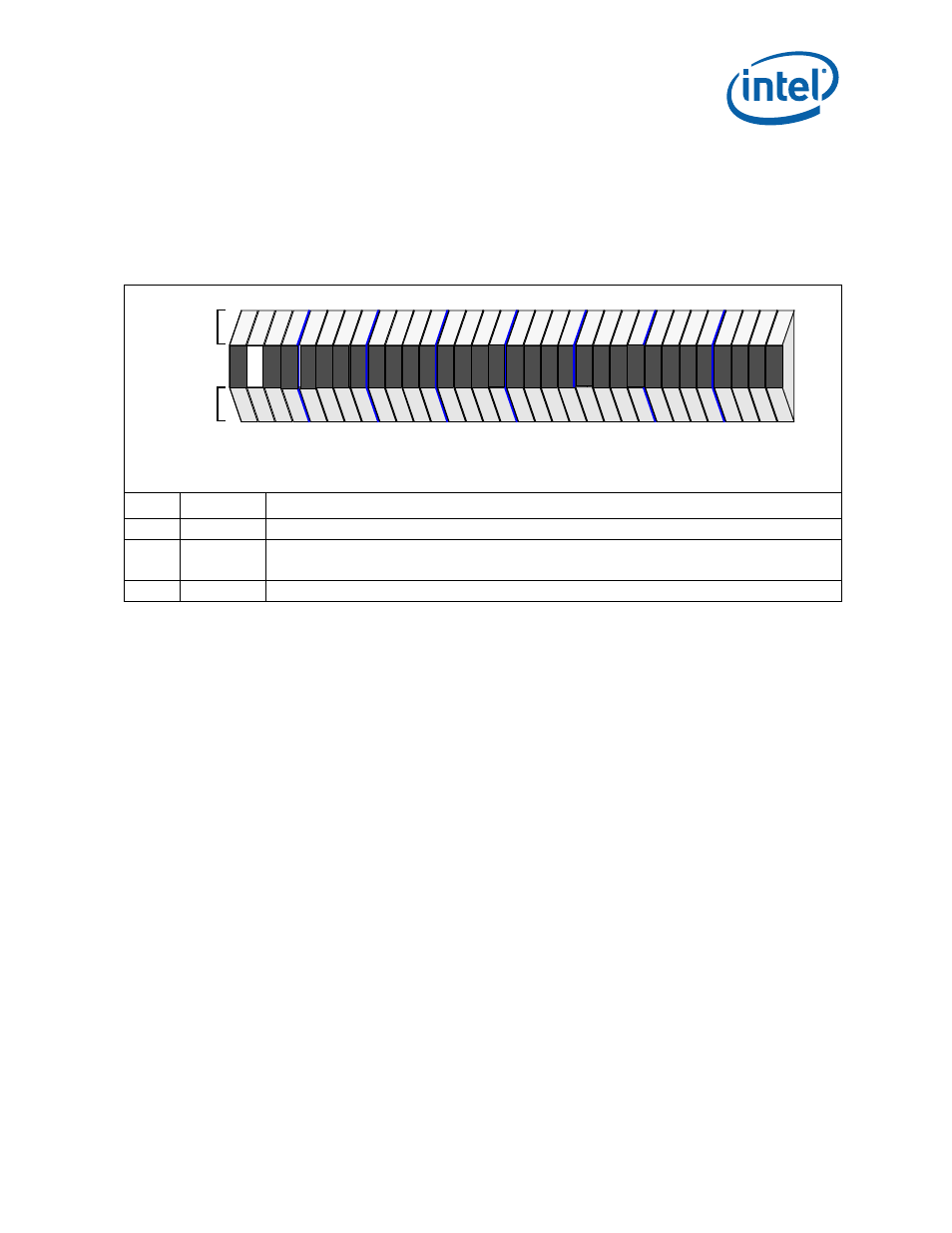

HostToLocal Byte Swap Control Register - H2L_BSCR

The LocalToHost Byte SWap Control Register (H2L_BSCR) provides the control to

enable/disable byte swapping.

Note:

The “Default” enables byte swapping.

Table 312. HostToLocal Byte Swap Control Register - H2L_BSCR

Bit

Default

Description

31

00

Reserved.

30

00

Byte Swap Disable - Read/Write

This bit must be set to prevent SDMA transfers from byte swapping.

29:0

00

Reserved.

Coprocessor

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

na

rw

rw

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal bus address offset

18250H