2 i2c acknowledge, Figure 96. acknowledge on the i2c bus, 96 acknowledge on the i – Intel CONTROLLERS 413808 User Manual

Page 699: Section 14.3.2, Section 14.3.2, “i2c, C acknowledge, Figure 96. acknowledge on the i, C bus, Every i, C bus protocol). the i

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

699

I

2

C Bus Interface Units—Intel

®

413808 and 413812

14.3.2

I

2

C Acknowledge

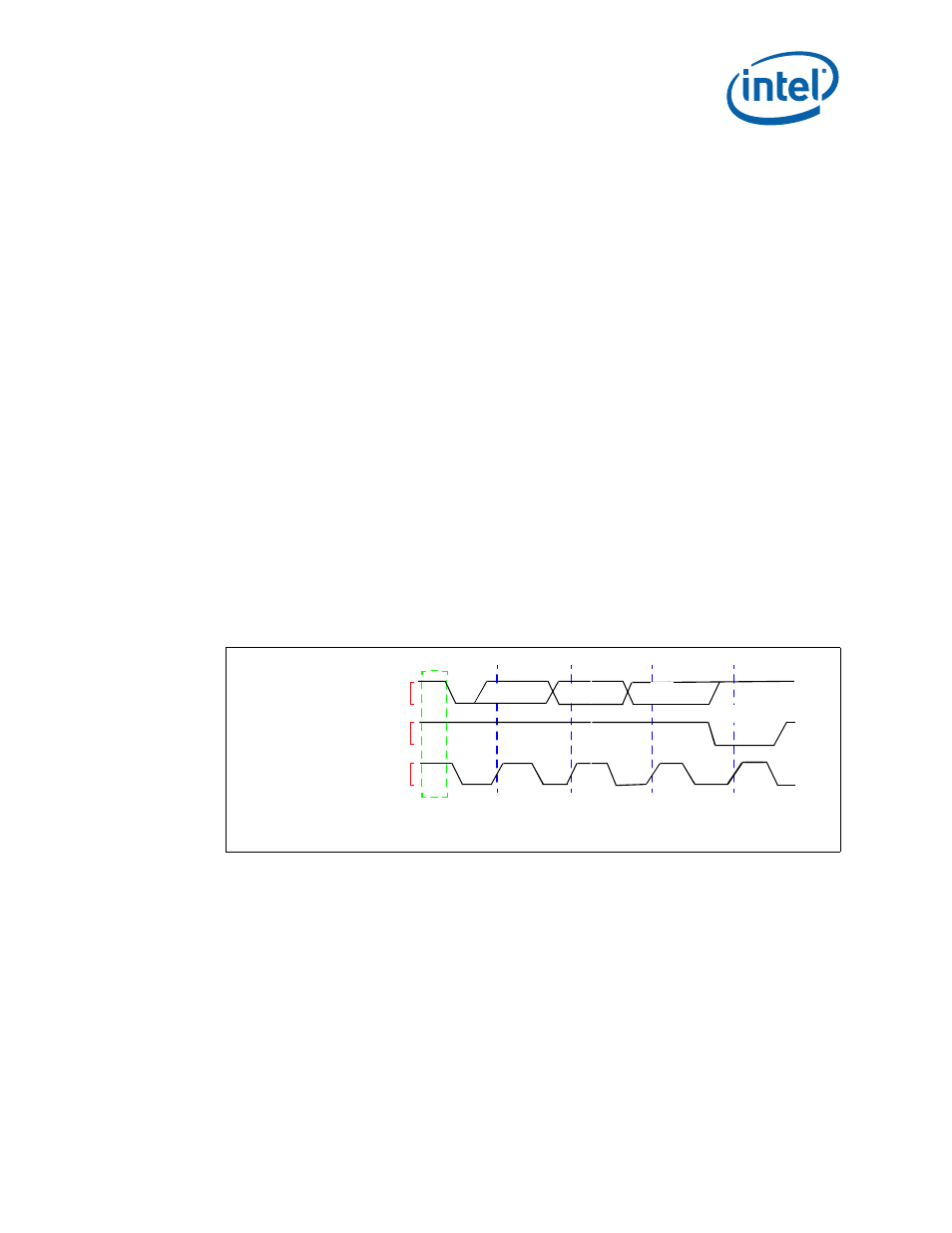

Every I

2

C byte transfer must be accompanied by an acknowledge pulse, which is

always generated by the receiver (master or slave). The transmitter must release the

SDA

line for the receiver to transmit the acknowledge pulse (see

In master-transmit mode, when the target slave receiver device cannot generate the

acknowledge pulse, the

SDA

line remains high. This lack of acknowledge (Nack) causes

the I

2

C unit to set the bus error detected bit in the ISR and generate the associated

interrupt (when enabled). The I

2

C unit aborts the transaction by generating a STOP

automatically.

In master-receive mode, the I

2

C unit signals the slave-transmitter to stop sending data

by using the negative acknowledge (Nack). The Ack/Nack bit value driven by the I

2

C

bus is controlled by the Ack/Nack bit in the ICR. The bus error detected bit in the ISR is

not set for a master-receive mode Nack (as required by the I

2

C bus protocol). The I

2

C

unit automatically transmits the Ack pulse, based on the Ack/Nack ICR bit, after

receiving each byte from the serial bus. Before receiving the last byte, software must

set the Ack/Nack Control bit to Nack. Nack is then sent after the next byte is received

to indicate the last byte.

In slave mode, the I

2

C unit automatically acknowledges its own slave address,

independent of the Ack/Nack bit setting in the ICR. As a slave-receiver, an Ack

response is automatically given to a data byte, independent of the Ack/Nack bit setting

in the ICR. The I

2

C unit sends the Ack value after receiving the eighth data bit of the

byte.

In slave-transmit mode, receiving a Nack from the master indicates the last byte is

transferred. The master then sends either a STOP or repeated START. The ISR’s unit

busy bit (2) remains set until a STOP or repeated START is received.

Figure 96. Acknowledge on the I

2

C Bus

1

2-7

8

9

SCL from Master

Data Output by Receiver (SDA)

Data Output by Transmitter (SDA)

Clock Pulse for

Acknowledge

SDA released

SDA pulled low by

Receiver (ACK)

Start Condition

~

~

~

~

~

~

~

~

B6286-01