Pci express uncorrectable error, Mask - errunc_msk, Pci express uncorrectable – Intel CONTROLLERS 413808 User Manual

Page 356: Error mask - errunc_msk, Pci express uncorrectable error mask - errunc_msk, Intel, Bit default description

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

356

Order Number: 317805-001US

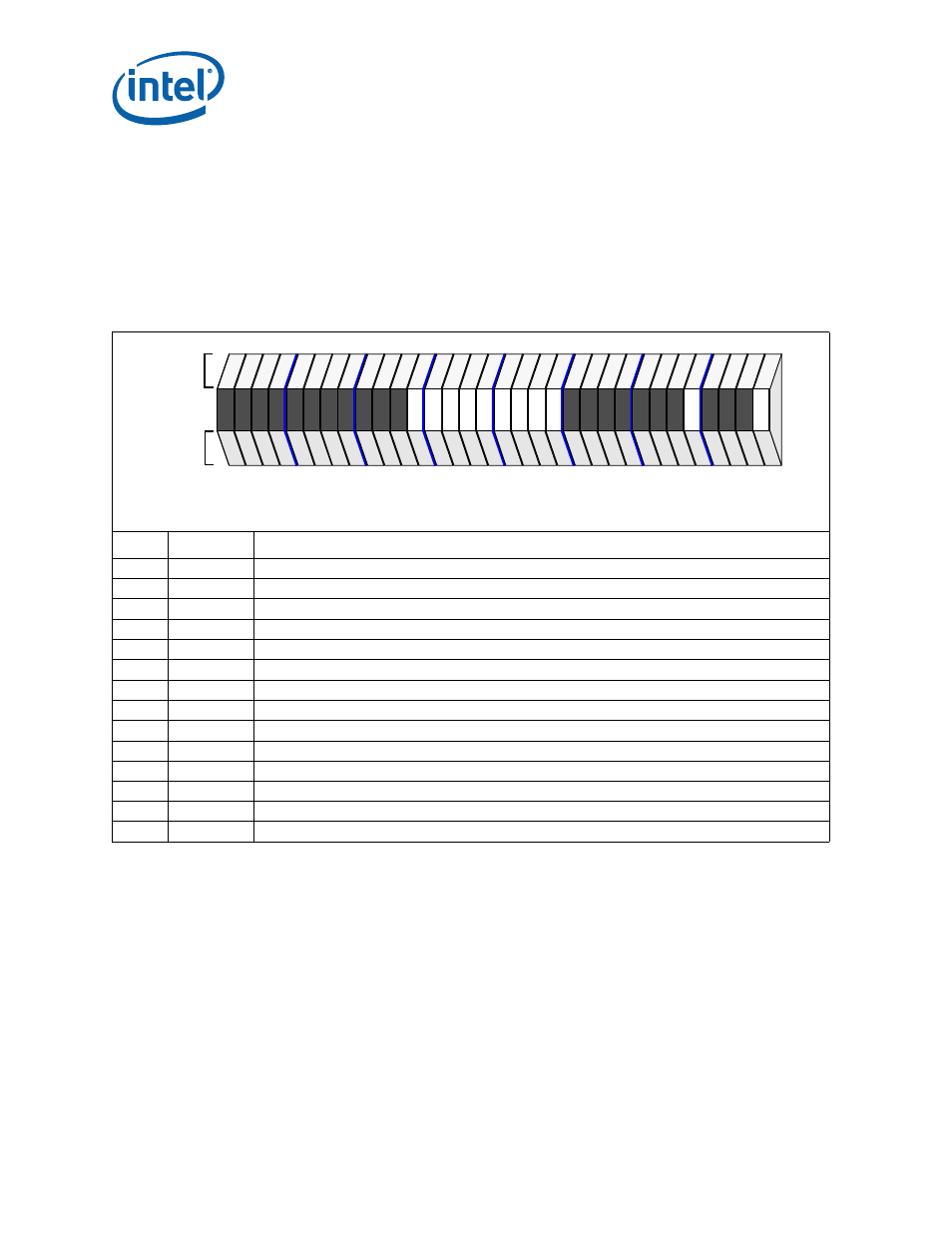

3.17.71 PCI Express Uncorrectable Error Mask - ERRUNC_MSK

The Uncorrectable Error Mask register controls reporting of individual errors by the

device to the PCI Express Root Complex via a PCI Express error message. A masked

error (respective bit set to 1b in the mask register) is not logged in the Header Log

register, does not update the First Error Pointer, and is not reported to the PCI Express

Root Complex by an individual device.

Note:

All bits in this register are sticky through reset.

Table 211. PCI Express Uncorrectable Error Mask - ERRUNC_MSK

Bit

Default

Description

31:21

0

Preserved.

20

0

Unsupported Request Error Status Error Mask - When ‘1’ error reporting is masked.

19

0

ECRC Check Error Mask - When ‘1’ error reporting is masked.

18

0

Malformed TLP Error Mask - When ‘1’ error reporting is masked.

17

0

Receiver Overflow Error Mask - When ‘1’ error reporting is masked.

16

0

Unexpected Completion Error Mask - When ‘1’ error reporting is masked.

15

0

Completer Abort Error Mask - When ‘1’ error reporting is masked.

14

0

Completion Time Out Error Mask - When ‘1’ error reporting is masked.:

13

0

Flow Control Protocol Error Status Error Mask - When ‘1’ error reporting is masked.

12

0

Poisoned TLP Received Error Mask - When ‘1’ error reporting is masked.

11:5

0

Preserved.

4

0

Data Link Protocol Error Mask - When ‘1’ error reporting is masked.

3:1

0

Preserved.

0

0

Training Error Mask - When ‘1’ error reporting is masked.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

rw

rw

pr

pr

pr

pr

pr

pr

rw

rw

S

S

S S S

S

S S

S

S

S

Attribute Legend:

RZ = Reserved Zero

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+108H