Figure 21 – Intel CONTROLLERS 413808 User Manual

Page 142

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

142

Order Number: 317805-001US

The first byte at the Extended Configuration Offset E8H is the Compact PCI Hot-Swap

Capability Identifier Register (

). This identifies this Extended

Configuration Header space as the type defined by the Compact PCI Hot-Swap

Specification, Revision 2.1.

Following the Capability Identifier Register is the single byte Next Item Pointer Register

) which indicates the configuration offset of an additional Extended

Capabilities Header, when supported. In the ATU, the Next Item Pointer Register is set

to 00H by default to indicate there are no additional Extended Capabilities Headers in

the ATU configuration space. Software can set this pointer to 90H indicating there is an

additional Extended Capabilities Headers supported in the ATUs configuration space.

The first byte at the Extended Configuration Offset 90H is the VPD Capability Identifier

Register (

). This identifies this Extended Configuration Header space as

the type defined by the PCI Local Bus Specification, Revision 2.3.

Following the Capability Identifier Register is the single byte Next Item Pointer Register

) which indicates the configuration offset of an additional Extended

Capabilities Header, when supported. In the ATU, the Next Item Pointer Register is set

to 00H indicating that there are no additional Extended Capabilities Headers supported

in the ATUs configuration space.

The following sections describe the ATU and Expansion ROM configuration registers.

Configuration space consists of 8, 16, 24, and 32-bit registers arranged in a predefined

format. Each register is described in functionality, access type (read/write, read/clear,

read only) and reset default condition.

All registers adhere to the definitions found in the PCI Local Bus Specification,

Revision 2.3 unless otherwise noted.

The Register Offset for PCI configuration registers is given in

. As stated, a

Type 0 configuration command on the bus, with an active

IDSEL

or a memory-mapped

internal bus access required to read or write these registers. The ATU is always located

at Function 0 in configuration space.

PCI Configuration command access to registers with offsets higher than 0FFH is not

supported.

Note:

In PCI-X Mode 2, the ATU handles all configuration command accesses to registers with

offsets higher than 0FFH as Reserved.

Note:

Each configuration register access type is individually defined for PCI configuration

accesses. Some PCI read-only configuration registers have read/write capability from

the 4138xx core CPU. See also

Chapter 19.0, “Peripheral Registers”

.

Figure 20. ATU Extended Configuration Header Format (Compact PCI Hot-Swap

Capability)

E8H

cPCI Capability ID

Next Item Pointer

Hot-Swap Ctrl/Status

Reserved

B6330-01

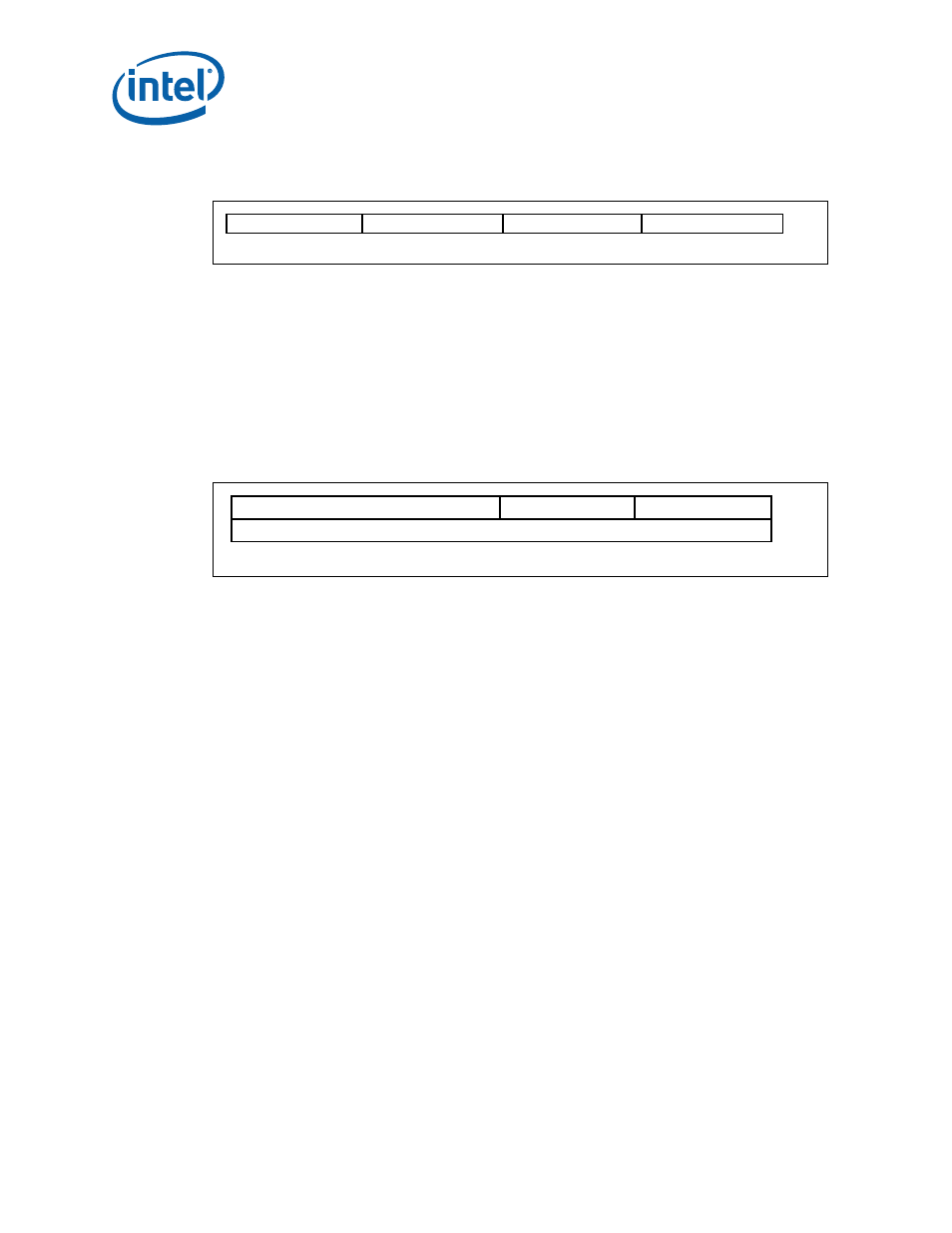

Figure 21. ATU Interface Extended Configuration Header Format (VPD Capability)

90H

94H

VPD Capability ID

Next Item Pointer

VPD Address

VPD Data

B6331-01