Intel, Bit default description, Writing a 1 to – Intel CONTROLLERS 413808 User Manual

Page 196

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

196

Order Number: 317805-001US

15:8

00H

Syndrome - The syndrome indicates information about the bit or bits that are in error, as described in

the PCI-X Protocol Addendum to the PCI Local Bus Specification, Revision 2.0.

Bit Syndrome

8 E0

9 E1

10 E2

11 E3

12 E4

13 E5

14 E6

15 E7 for 64-bit data, 0b for 32-bit data

7

0

2

ECC Error Corrected - When the ECC Error Phase register is non-zero, this bit indicates whether the

error that was captured was corrected. Correctable ECC errors that occur while error correction is

enabled (see Disable ECC Correction bit) are the only errors that are corrected. When the ECC Error

Phase register is zero, this bit is undefined.

0 = The error that was captured was not corrected.

1 = The error that was captured was corrected.

6:4

000

2

ECC Error Phase - When the 4138xx detects either a correctable or uncorrectable ECC error, this register

indicates in which phase of the transaction the error occurred, and for data phase errors whether it was

a 32-bit data error (seven-bit ECC) or 64-bit data error (eight-bit ECC). When this register is set to 0,

the 4138xx is enabled to latch information about an ECC error. When the 4138xx detects an error, it

latches the phase of the error in this register, and stores status information for the error in this register

and in the ECC Address, and ECC Attribute registers.

Register ECC Error Phase

0 No Error

1 First 32 bits of address

2 Second 32 bits of address

3 Attribute phase

4 32 data phase

5 64 bit data phase

6 Reserved

7 Reserved

Note:

Writing a 1 to

any

of these bits clears this register and enables the device to capture the next

error.

3

0

2

Additional Uncorrectable ECC Error - This bit is set when the 4138xx detects an uncorrectable ECC error,

or a correctable ECC error while error correction is disabled, and the device is already indicating some

other ECC error (i.e. the ECC Error Phase register is non-zero).

0 = No additional uncorrectable ECC error has been detected.

1 = One or more additional uncorrectable ECC errors have been detected.

Table 84. ECC Control and Status Register - ECCCSR (Sheet 2 of 3)

Bit

Default

Description

PCI

IOP

Attributes

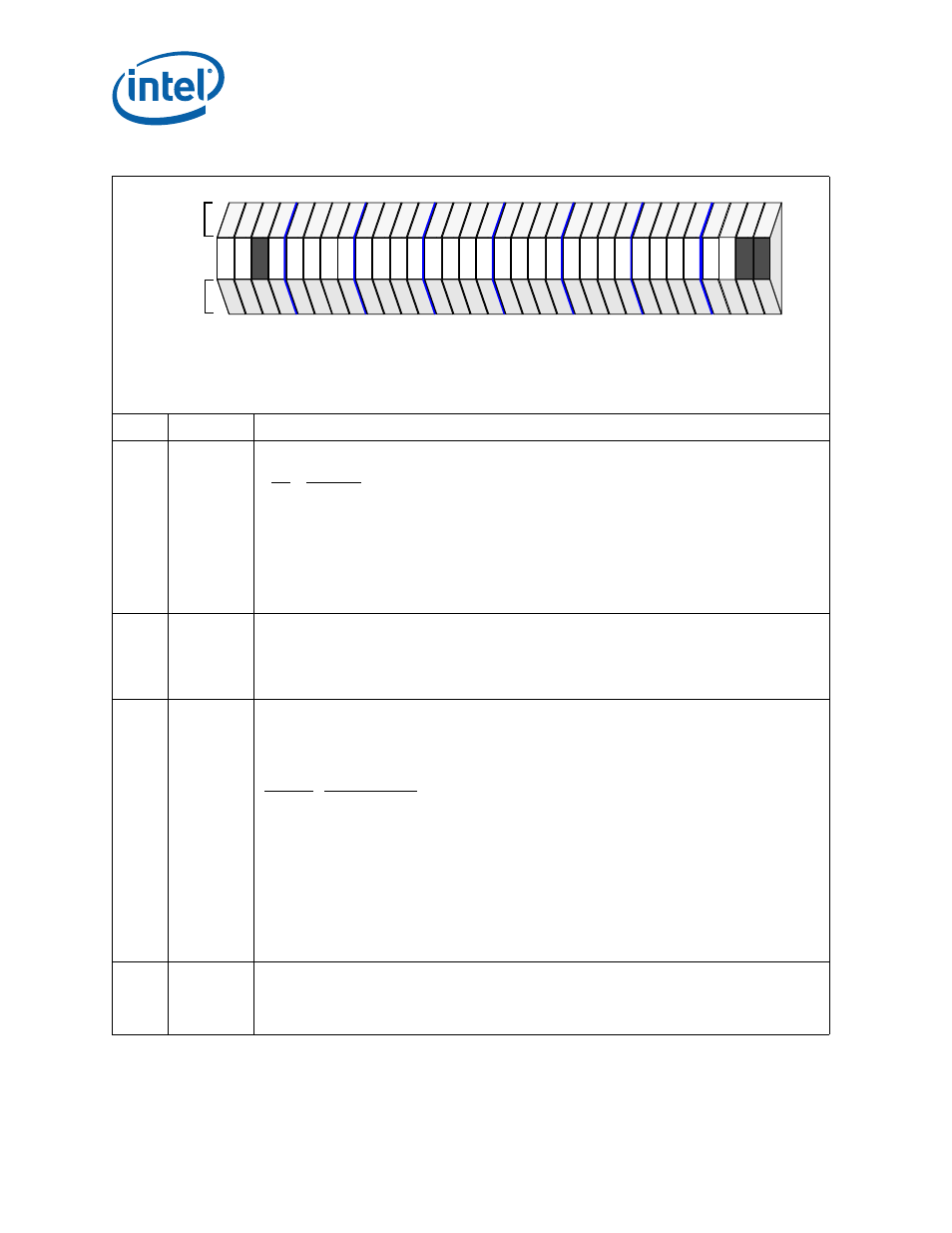

Attributes

28

24

20

16

12

8

4

0

31

ro

ro

rw

rw

rv

rv

wo

wo

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

rc

rc

rc

rc

rc

rc

rc

rc

rc

rc

rv

rv

rv

rv

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

WO = Write Only

NA = Not Accessible

Internal Bus Address

+0D8H