3 transaction ordering, Table 129. atu inbound data flow ordering rules, 129 atu inbound data flow ordering rules – Intel CONTROLLERS 413808 User Manual

Page 264: Section 3.8.3

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

264

Order Number: 317805-001US

3.8.3

Transaction Ordering

Because the ATU can process multiple transactions, they must maintain proper

ordering to avoid deadlock conditions and improve throughput. The ATU transaction

ordering rules used by the 4138xx are listed in

for the inbound direction and

for the outbound direction. The tables are based on the

direction the transaction is moving, i.e. the data for inbound completion moves in the

same direction as the data for an inbound write or the address/command for an

inbound read.

Note:

Outbound Non-Posted Writes are the result of Internal Bus Memory writes that are

claimed by either the I/O translation window or the

Outbound Configuration Cycle Data

. Though these write requests arrive on the PCI Express Link as

non-posted write requests, it is important to note that from the Intel XScale

®

processor’s point of view, these internal bus memory write requests are posted into the

Outbound ATU transaction queue. Thus, even though a write completion is returned to

the ATU on the PCI Express Link for outbound non-posted write request, the write

completion is not passed back through to the internal bus. Additionally, strong ordering

between outbound memory (posted) write requests and outbound non-posted write

requests are

not

maintained as indicated in

For best performance, the user should designate the two Outbound Memory Windows

as non-cachable and bufferable from theIntel XScale

®

processor. This assignment

enables the Intel XScale

®

processor to issue multiple outstanding transactions to the

Outbound Memory Windows, thereby, taking full advantage of the ATU outbound queue

architecture. However, the user needs to be aware that the Outbound ATU queue

architecture does not maintain strict ordering between read and write requests as

described in

Table 130, “ATU Outbound Data Flow Ordering Rules” on page 265

. In the

event that the user requires strict ordering to be maintained, the user must change the

designation of this region of memory to be non-cachable/non-bufferable and enforce

the requirement in software.

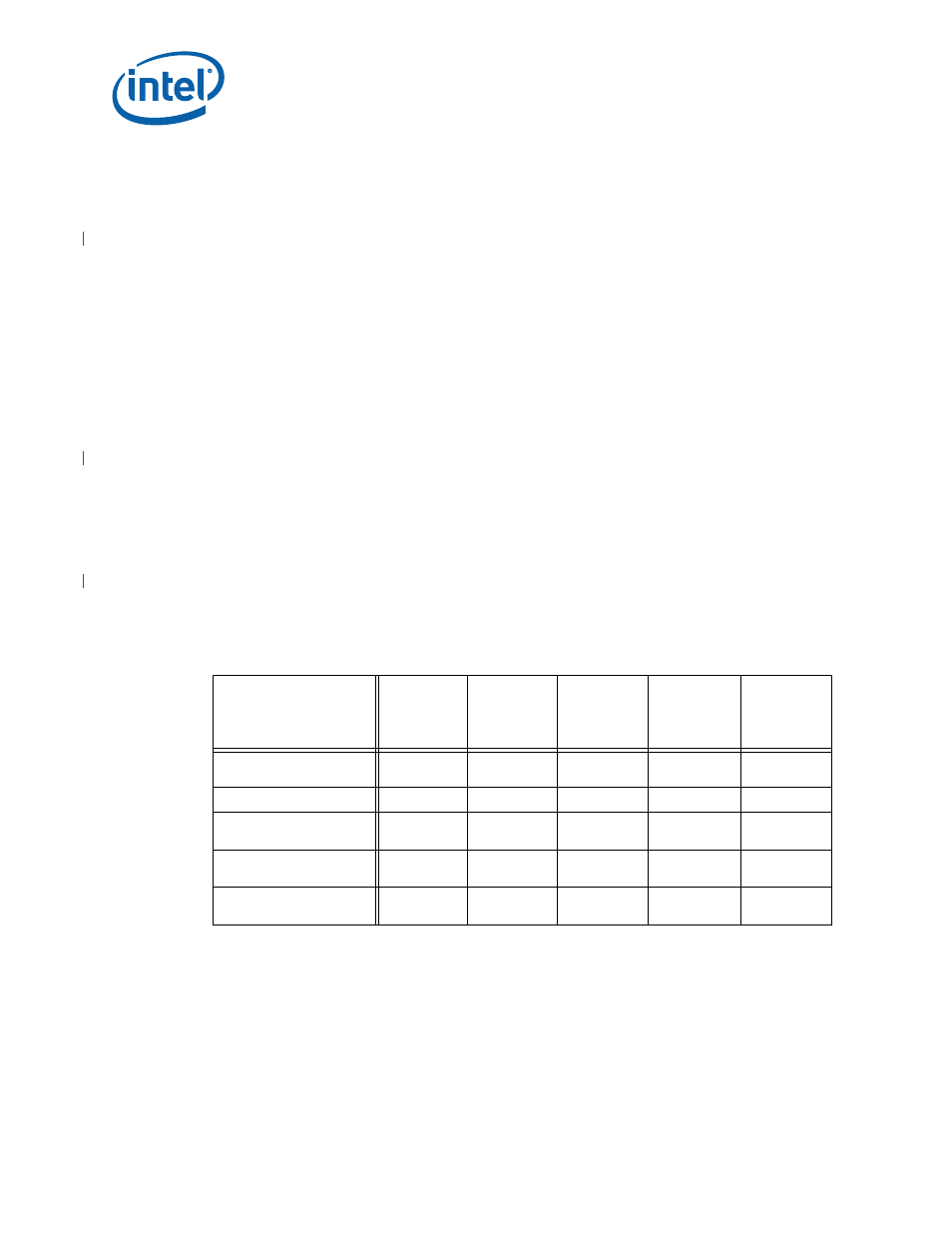

Table 129. ATU Inbound Data Flow Ordering Rules

Row Pass Column?

Inbound

Write or

Message

Request

Inbound

Read

Request

Inbound

Configuratio

n Write

Request

Inbound

Read

Completion

Inbound

Configuratio

n or I/O

Write

Completion

Inbound Write or

Message Request

No

Yes

Yes

Yes

Yes

Inbound Read Request

No

No

No

Yes

Yes

Inbound Configuration

Write Request

No

No

No

Yes

Yes

Inbound Read

Completion

No

Yes

Yes

Yes?

Yes?

Inbound Configuration

or I/O Write Completion

a

a. Inbound Completions for Configuration writes and I/O writes are not applicable since these transactions are

never passed back to the Internal Bus Requester (Intel XScale

®

processor). The reason is that from the Intel

XScale

®

processor’s point of view, these write requests are posted into the Outbound ATU transaction queue.

N/A

N/A

N/A

N/A

N/A