6 north internal bus events, Table 503. north internal bus initiator events, 502 north internal bus source select summary – Intel CONTROLLERS 413808 User Manual

Page 761: 503 north internal bus initiator events, Pmon, Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

761

PMON Unit—Intel

®

413808 and 413812

16.5.7.6 North Internal Bus Events

The North Internal Bus has multiple initiators. Some events apply to each requester

unit and the following table represents the Source Select Field values for each unit.

The events and corresponding codes for the North Internal Bus are defined in the

following table. These codes are unique to the IOP programming model of the

PMON

unit.

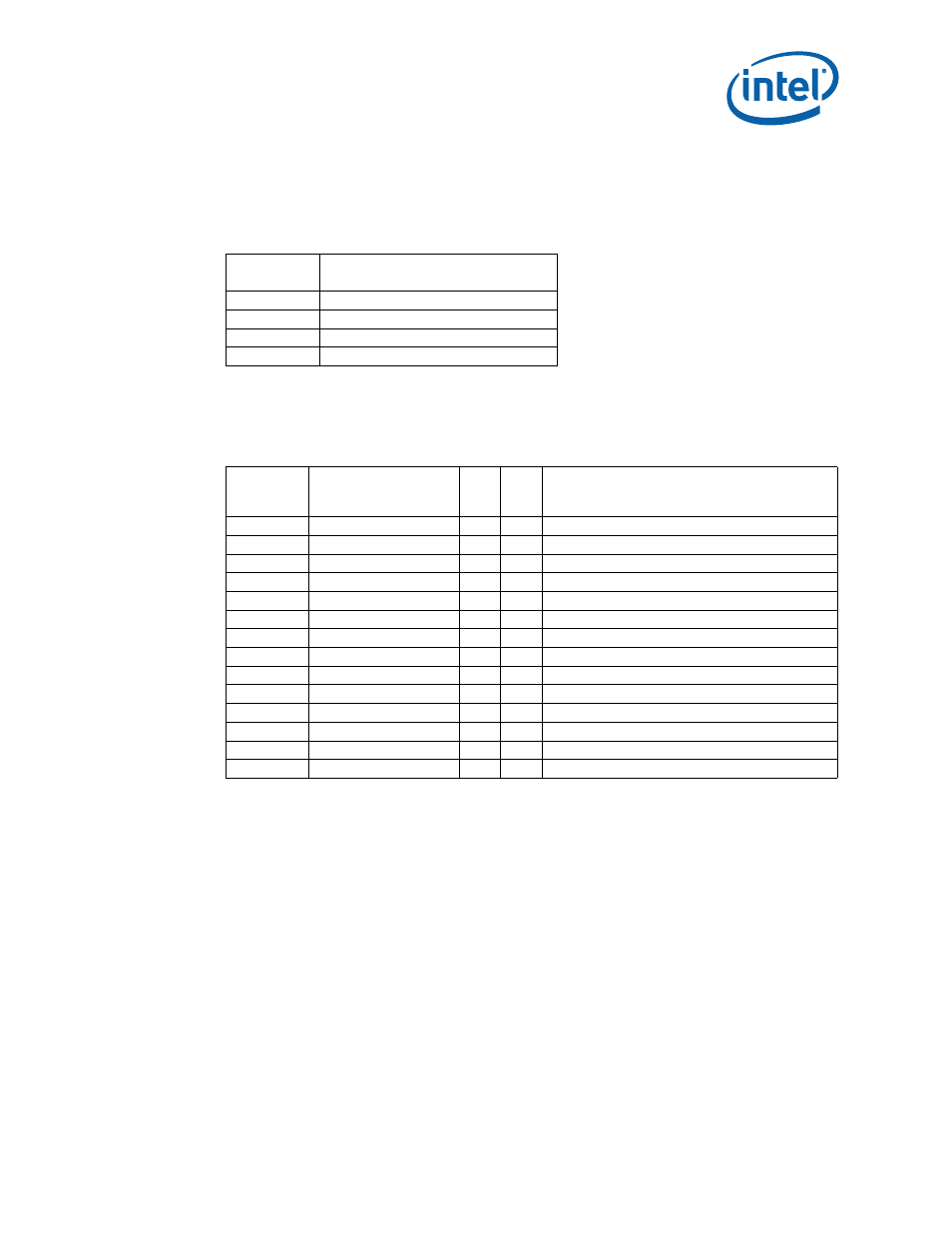

Table 502. North Internal Bus Source Select Summary

Source Select

Value

Port

0

Intel XScale

®

core 0

1

Intel XScale

®

core 1

2

Internal Bus Bridge

3:7

Reserved

Table 503. North Internal Bus Initiator Events

Event

Selection

Code

Event

SRC Type Comment

800

NIB Addr Acq

Y

D Address Acquisition Duration

801

NIB Addr Gnt

Y

O Address Grants Received

802

NIB Data Acq

Y

D Data Acquisition Duration

803

NIB Data Gnt

Y

O Data Grants Received

804-807

Reserved

808

NIB Snoop Retry

Y

O # Transactions which receive a Snoop Retry

809

NIB Coherent Requests

Y

O # Requests in Coherent Memory (XSI Bridge only)

80A-80F

Reserved

810

NIB Reads

Y

O # Read Transactions

811

NIB Read Data

Y

D # Read Data Cycles (in 16-Bytes)

812 - 81F Reserved

820

NIB Writes

Y

O # Write Transactions

821

NIB Write Data

Y

D # Write Data Cycles (in 16-Bytes)

822 - 87F Reserved