6 pbi base address register 1 - pbbar1, Table 369. pbi base address register 1 - pbbar1, 6 pbi base address register 1 — pbbar1 – Intel CONTROLLERS 413808 User Manual

Page 559: 369 pbi base address register 1 — pbbar1, Peripheral bus interface unit—intel, Bit default description

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

559

Peripheral Bus Interface Unit—Intel

®

413808 and 413812

9.3.6

PBI Base Address Register 1 — PBBAR1

The PBI Base Address Register 1 (PBBAR1) defines the block of memory addresses

where PBI Memory Window 1 begins. The PBBAR1 defines the base address and

describes the required memory block size; see

Section 9.3.3, “Determining Block Sizes

for Memory Windows” on page 556

. The selected base address needs to be naturally

aligned to the granularity of the memory block size. For instance, when a 64 Kbyte

memory window size is selected, the base address needs to be 64 Kbyte address

aligned (i.e., bits 15:12 of the base address are required to be 000b).

Bits 1:0 define the PBI bus width for PBI Memory Window 1.

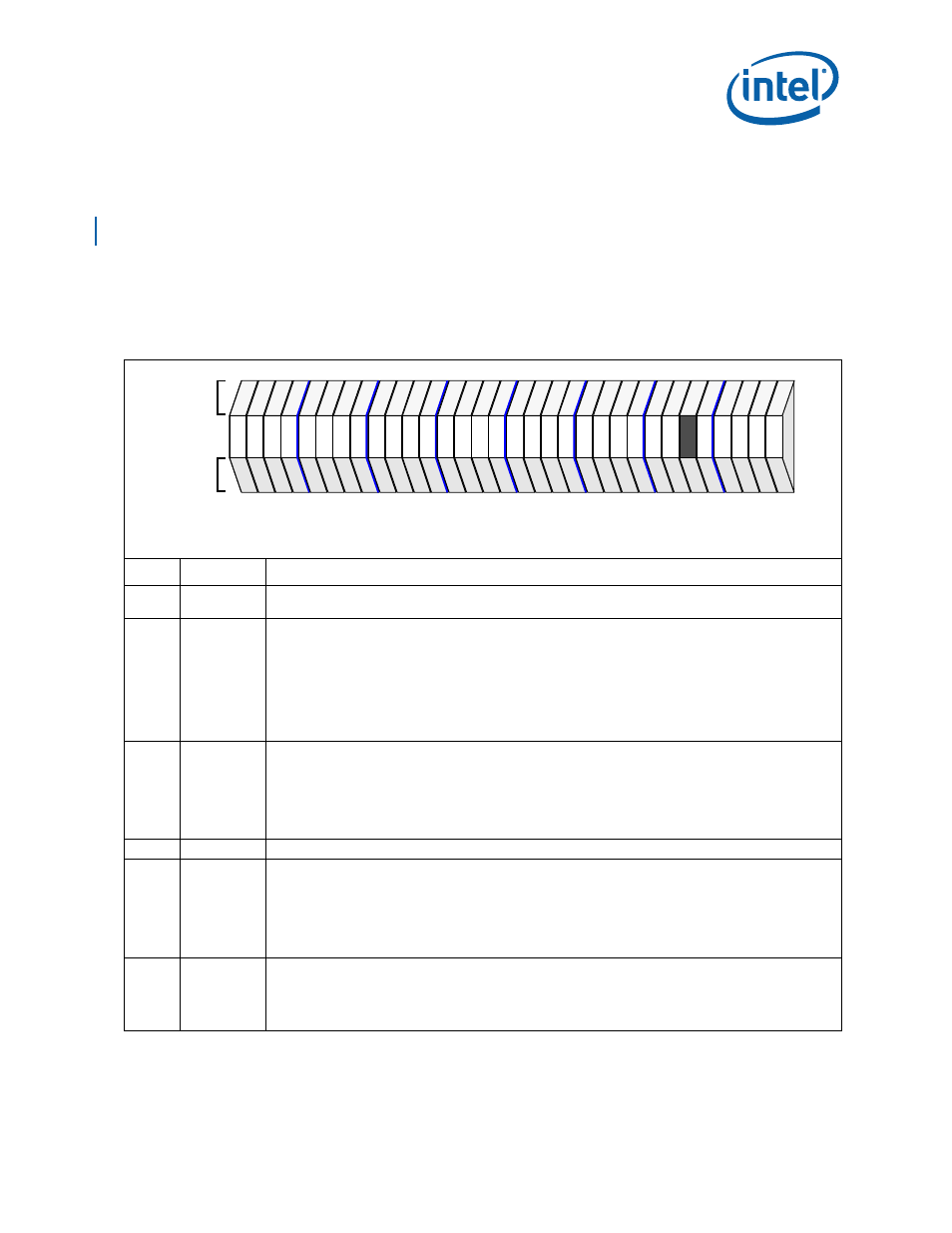

Table 369. PBI Base Address Register 1 — PBBAR1

Bit

Default

Description

31:12

00000H

Memory Window 1 Base Address: These bits define the actual location the PBI responds to for accesses

to Memory Window 1.

11:09

001

2

Data-to-Data Wait States: Defines the number of data-to-data wait states for the Peripheral window

during a burst read transaction.

00X - Wait states are equal to the programmed value in the Address-to-Data Wait States field.

010 - 4 Data-to-Data wait states

011 - 8 Data-to-Data wait states

100 - 12 Data-to-Data wait states

101 - 16 Data-to-Data wait states

Others - 20 Data-to-Data wait states

Note:

By default, data-to-data wait states are 20, since it is the same as address-to-data wait states.

08:06

111

2

Recovery Cycle Wait States: Defines the number of recovery cycle wait states for the Peripheral window.

000 - 1 Recovery wait state

001 - 4 Recovery wait states

010 - 8 Recovery wait states

011 - 12 Recovery wait states

100 - 16 Recovery wait states

Others (Default) - 20 Recovery wait states

05

0

2

Reserved

04:02

111

2

Address-to-Data Wait States: Defines the number of address-to-data wait states for the Peripheral

window during a read or write transaction.

000 - 4 Address-to-Data wait states

001 - 8 Address-to-Data wait states

010 - 12 Address-to-Data wait states

011 - 16 Address-to-Data wait states

Others (Default) - 20 Address-to-Data wait states

01:00

00

2

Bus Width: Defines the bus width for this Memory Window:

00 - 8 bits wide

01 - 16 bits wide

10 - Reserved

11 - Reserved

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rv

na

rw

na

rw

na

rw

na

rw

na

rw

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Intel XScale

®

processor Local Bus Address

Offset

+1590H