4 register descriptions, Table 445. uart unit registers, 444 uart register addresses as offsets of a base – Intel CONTROLLERS 413808 User Manual

Page 668: 445 uart unit registers

Intel

®

413808 and 413812—UARTs

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

668

Order Number: 317805-001US

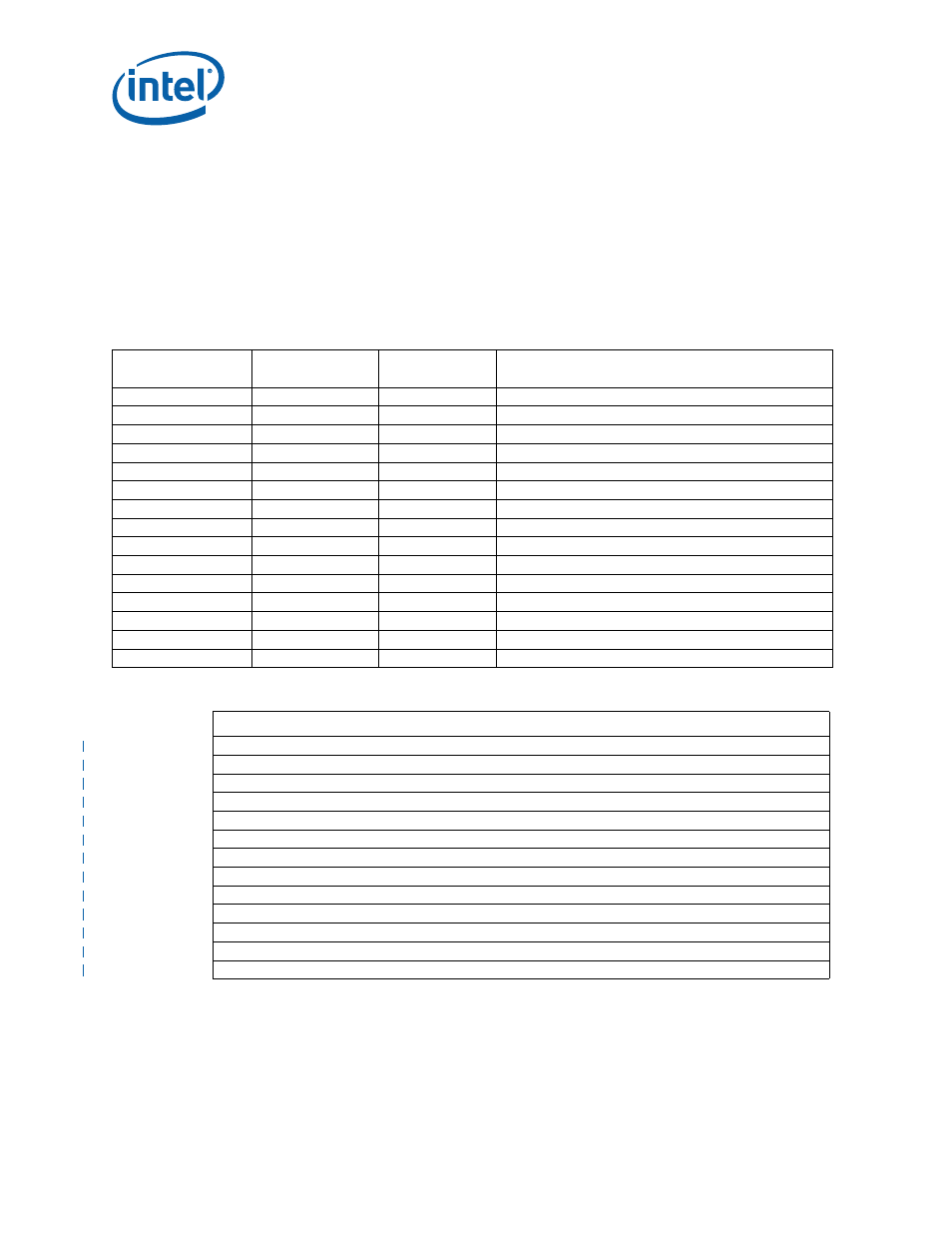

13.4

Register Descriptions

There are 15 registers in each UART. The registers are all 32 bit registers, but only

lower 8 bits have valid data. The 12 UART registers share eight address locations in the

MMR address space. Table 444 shows the registers and their addresses as offsets of a

base address. The base address for each UART is 32 bits and is internal bus address

offset 2300H for UART 0, and 2340H for UART 1. Note that the state of the Divisor

Latch Bit (DLAB), which is the MOST significant bit of the Serial Line Control Register,

affects the selection of certain of the UART registers. The DLAB bit must be set high by

the system software to access the Baud Rate Generator Divisor Latches.

Table 444. UART Register Addresses as Offsets of a Base

UART Register

Addresses

DLAB Bit Value

Name

Register Accessed

Base

0

UxRBR

UART x Receive BUFFER (read only)

Base

0

UxTHR

UART x Transmit BUFFER (write only)

Base + 04H

0

UxIER

UART x Interrupt Enable (R/W)

Base + 08H

X

UxIIR

UART x Interrupt I.D. (read only)

Base + 08H

X

UxFCR

UART x FIFO Control (write only)

Base + 0CH

X

UxLCR

UART x Line Control (R/W)

Base + 10H

X

UxMCR

UART x Modem Control (R/W)

Base + 14H

X

UxLSR

UART x Line Status (Read only)

Base + 18H

X

UxMSR

UART x Modem Status (Read only)

Base + 1CH

X

UxSPR

UART x Scratch Pad (R/W)

Base

1

UxDLL

UART x Divisor Latch (Low Byte, R/W)

Base + 04H

1

UxDLH

UART x Divisor Latch (High Byte, R/W)

Base + 24H

X

UxFOR

UART x FIFO Occupancy Register (R/W)

Base + 28H

X

UxABR

UART x Autobaud Control Register (R/W)

Base + 2CH

X

UxACR

UART x Autobaud Count Register (read only)

Table 445. UART Unit Registers

Section, Register Name, Acronym, page

Section 13.4.1, “UART x Receive Buffer Register” on page 670

Section 13.4.2, “UART x Transmit Holding Register” on page 670

Section 13.4.3, “UART x Interrupt Enable Register” on page 671

Section 13.4.4, “UART x Interrupt Identification Register” on page 672

Section 13.4.5, “UART x FIFO Control Register” on page 674

Section 13.4.6, “UART x Line Control Register” on page 676

Section 13.4.7, “UART x Modem Control Register” on page 678

Section 13.4.8, “UART x Line Status Register” on page 680

Section 13.4.9, “UART x Scratchpad Register” on page 684

Section 13.4.10, “Divisor Latch Registers” on page 685

Section 13.4.11, “UART x FIFO Occupancy Register” on page 686

Section 13.4.12, “UART x Auto-Baud Control Register” on page 687

Section 13.4.13, “UART x Auto-Baud Count Register” on page 688