Intel CONTROLLERS 413808 User Manual

Page 823

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

823

Peripheral Registers—Intel

®

413808 and 413812

Co

re

Pe

rfo

rm

an

ce

M

on

ito

rin

g U

nit

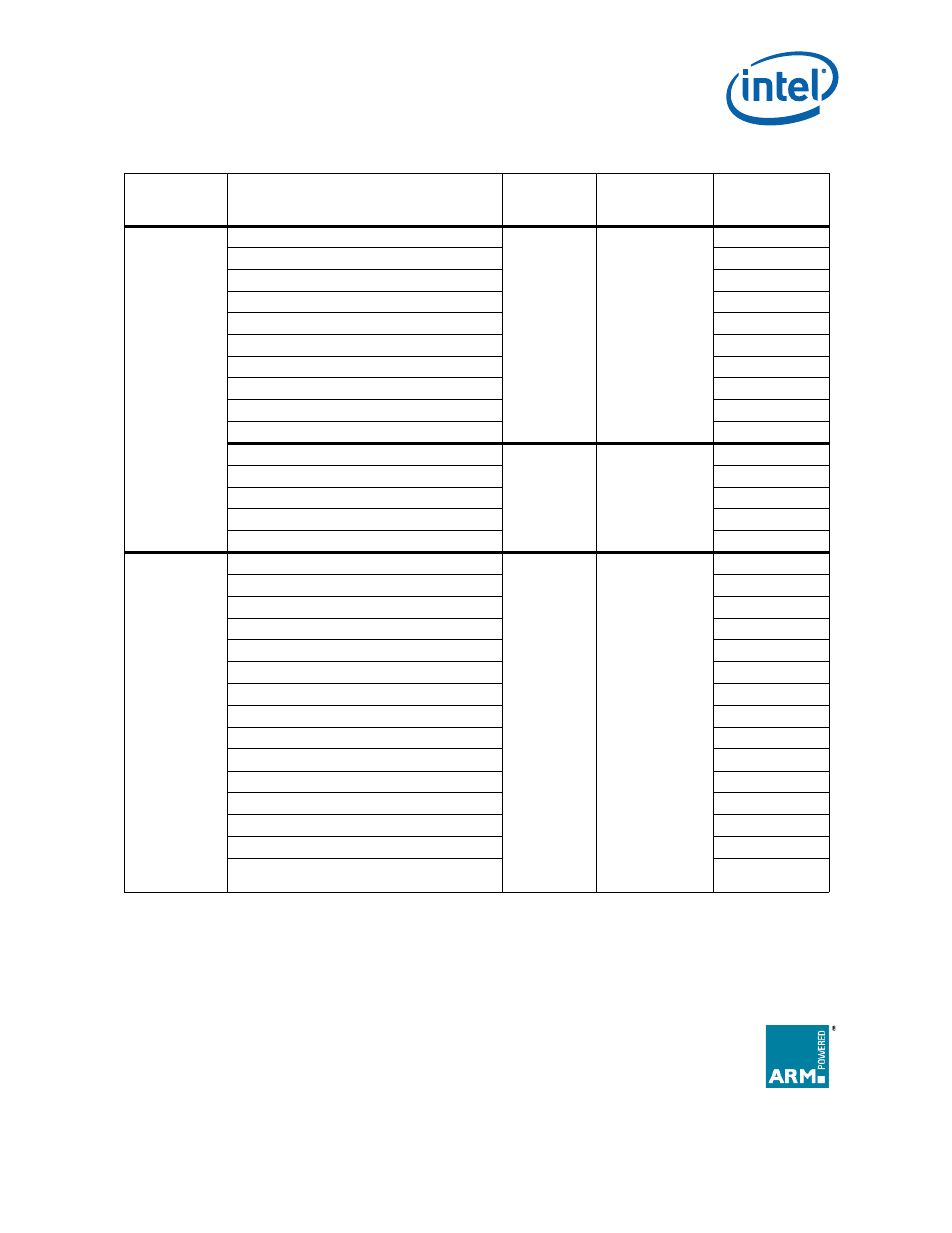

Performance Monitor Control Register

CP14

1

Register 0

Clock Count Register

Register 1

Undefined

Register 2

Undefined

Register 3

Interrupt Enable Register

Register 4

Overflow Flag Register

Register 5

Undefined

Register 6

Undefined

Register 7

Event Selection Register

Register 8

Undefined

Register 9–15

Performance Count Register 0

CP14

2

Register 0

Performance Count Register 1

Register 1

Performance Count Register 2

Register 2

Performance Count Register 3

Register 3

Undefined

Register 4–15

Sy

ste

m

Co

ntr

ols

ID & Cache Type Registers

CP15

CP 15 Function

a

Register 0

Control and Auxiliary Control Registers

Register 1

Translation Table Base Register

Register 2

Domain Access Control Register

Register 3

Undefined

Register 4

Fault Status Register

Register 5

Fault Address Register

Register 6

Cache Functions Register

Register 7

TLB Operations Register

Register 8

Cache Lock Down

Register 9

TLB Lock Down

Register 10

Reserved

Register 11–12

Process ID Register

Register 13

Breakpoint Registers

Register 14

CP Access (PID) Coprocessor Access Control

Register

Register 15

a. Some of the CP15 registers are differentiated by the Opcode_2 field. For CP15, the CR

m

is used in some cases to denote

different control functions for a given coprocessor register rather than a distinct register decode. Please refer to the

Intel

®

80200 Processor based on Intel

®

XScale™ Microarchitecture Developer’s Manual

(Order Number: 273411), for more details

on the operation of CP15.

Table 549. Coprocessor Register Locations (Sheet 4 of 4)

Peripheral

Register Description (Name)

Coprocessor

Field CR

m

Coprocessor

Register

(Field CR

n

)