Intel, Bit default description – Intel CONTROLLERS 413808 User Manual

Page 374

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

374

Order Number: 317805-001US

3.17.95 Outbound Upper 32-bit Memory Window Translate Value

Register 0 - OUMWTVR0

The Outbound Upper 32-bit Memory Window Translate Value Register 0 (OUMWTVR0)

defines the upper 32-bits of address used during a dual address cycle. This enables the

outbound ATU to directly address anywhere within the 64-bit host address space. When

this register is all-zero, then a 3DW header is generated on the PCI Express Link.

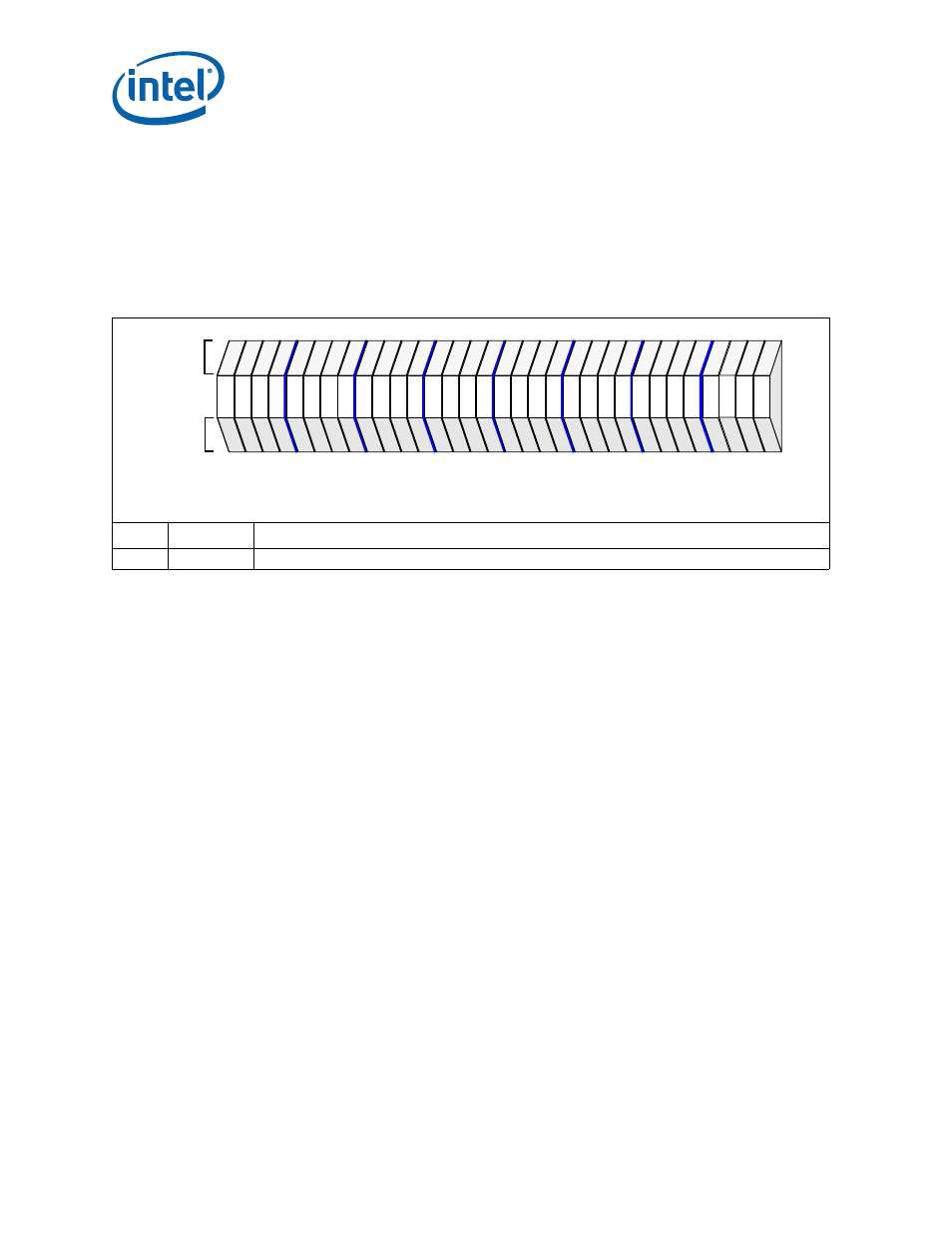

Table 235. Outbound Upper 32-bit Memory Window Translate Value Register 0-

OUMWTVR0

Bit

Default

Description

31:00 0000 0000H These bits define the upper 32-bits of address driven during the dual address cycle (DAC).

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+30CH