8 uart x line status register, 455 uart x line status register - (uxlsr) – Intel CONTROLLERS 413808 User Manual

Page 680

Intel

®

413808 and 413812—UARTs

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

680

Order Number: 317805-001US

13.4.8

UART x Line Status Register

This register provides status information to the processor concerning the data

transfers. Bits 5 and 6 show information about the transmitter section. The remainder

of the bits contain information about the receiver.

In non-FIFO mode, three of the LSR register bits, parity error, framing error, and break

interrupt, show the error status of the character that has just been received. In FIFO

mode, these three status bits are stored with each received character in the FIFO. LSR

shows the status bits of the character at the bottom of the FIFO. When the character at

the bottom of the FIFO has errors, the LSR error bits are set and are not cleared until

software reads LSR, even when the character in the FIFO is read and a new character is

now at the bottom of the FIFO.

Bits 1 through 4 are the error conditions that produce a Receiver Line Status Interrupt

when any of the corresponding conditions are detected and the interrupt is enabled.

These bits are not cleared by reading the erroneous byte from the FIFO or receive

buffer. They are cleared only by reading LSR. In FIFO mode, the Line Status Interrupt

occurs only when the erroneous byte is at the bottom of the FIFO. When the erroneous

byte being received is not at the bottom of the FIFO, an interrupt is generated only

after the previous bytes are read and the erroneous byte is moved to the bottom of the

FIFO.

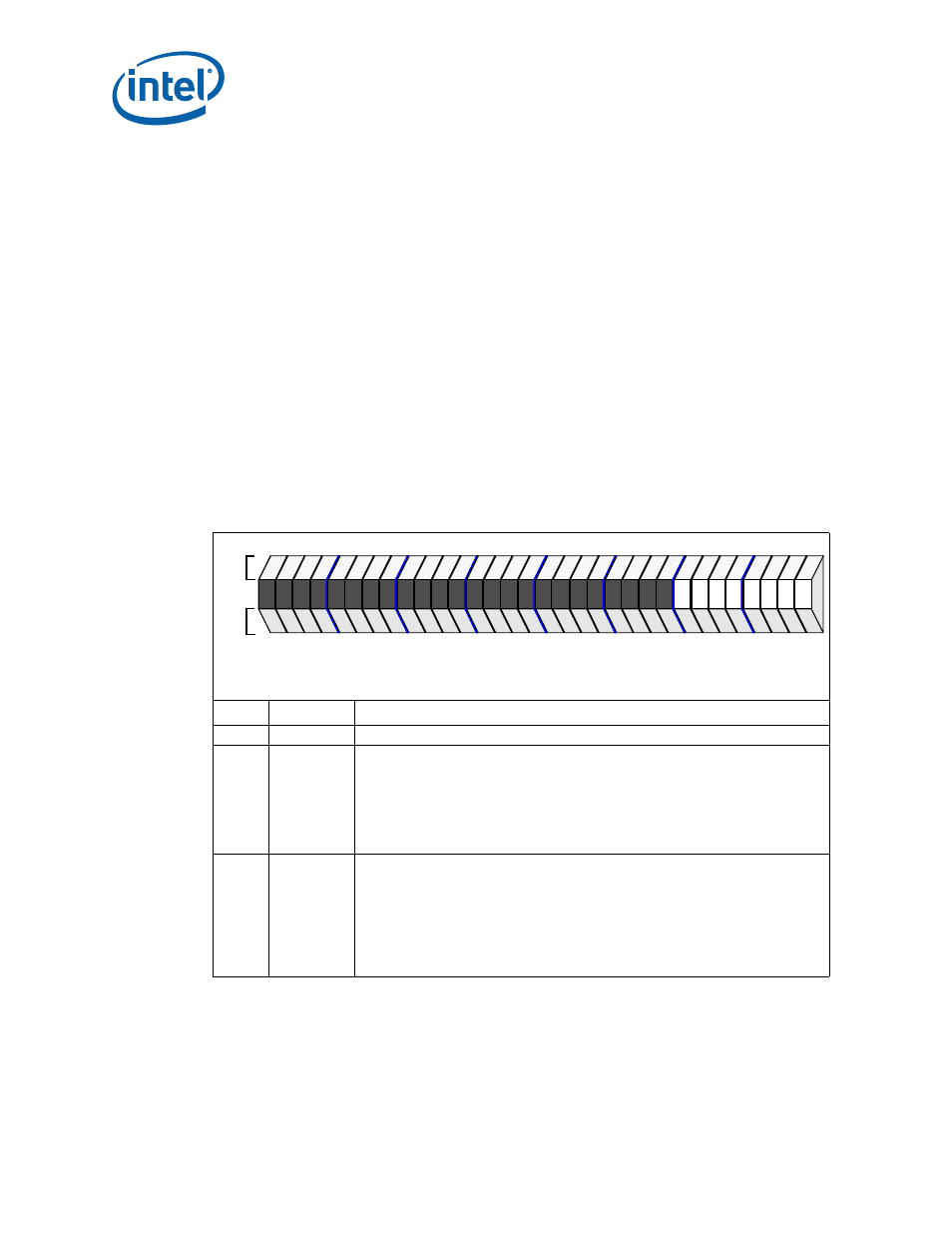

Table 455. UART x Line Status Register - (UxLSR) (Sheet 1 of 3)

Bit

Default

Description

31:8

00 0000h

Reserved

7

0

2

FIFO Error Status (FIFOE): In non-FIFO mode, this bit is clear (0). In FIFO Mode,

this bit is set (1) when there is at least one parity error, framing error, or break

indication for any of the characters in the FIFO. A processor read to the Line Status

register does not reset this bit. FIFOE is reset when all error bytes have been read

from the FIFO. FIFOE being set to 1 does NOT generate an interrupt.

0 = No errors exit in the receive FIFO

1 = At least one character in receiver FIFO has errors

6

1

2

Transmitter Empty (TEMT): Set (1) when the Transmit Holding register and the

Transmitter Shift register are both empty. It is reset to zero (0) when either the

Transmit Holding register or the Transmitter Shift register contains a data character.

In FIFO mode, TEMT is set to 1 when the transmitter FIFO and the Transmit Shift

register are both empty.

0 = There is data in the Transmit Shift register, the Transmit Holding register, or the

FIFO

1 = All the data in the transmitter has been shifted out

PC

I

IO

P

A

tt

ri

bu

te

s

A

tt

ri

bu

te

s

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

ro

na

Unit #

01

Intel XScale

®

Core internal bus address

+2314H (DLAB=x)

+2354H (DLAB=x)

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible