Cirrus Logic EP93xx User Manual

Page 93

DS785UM1

3-23

Copyright 2007 Cirrus Logic

MaverickCrunch Co-Processor

EP93xx User’s Guide

3

3

3

Mnemonic:

Bit Definitions:

N:

Floating point precision - 0 for single, 1 for double.

Rn:

Base register in ARM

CRd: Source

register.

Store Integer Values to Memory

Description:

Stores a 32- or 64-bit integer value from a MaverickCrunch register into

memory.

Mnemonic:

Bit Definitions:

N:

Integer width - 0 for 32-bit integer, 1 for 64-bit integer

Rn:

Base register in ARM

CRd: Source

register.

Table 3-13. Mnemonic Codes for Storing Floating Point Values to Memory

Mnemonic

Addressing Mode

N

CFSTRS

Immediate pre-indexed

0

CFSTRS

Immediate post-indexed

0

CFSTRD

Immediate pre-indexed

1

CFSTRD

Immediate post-indexed

1

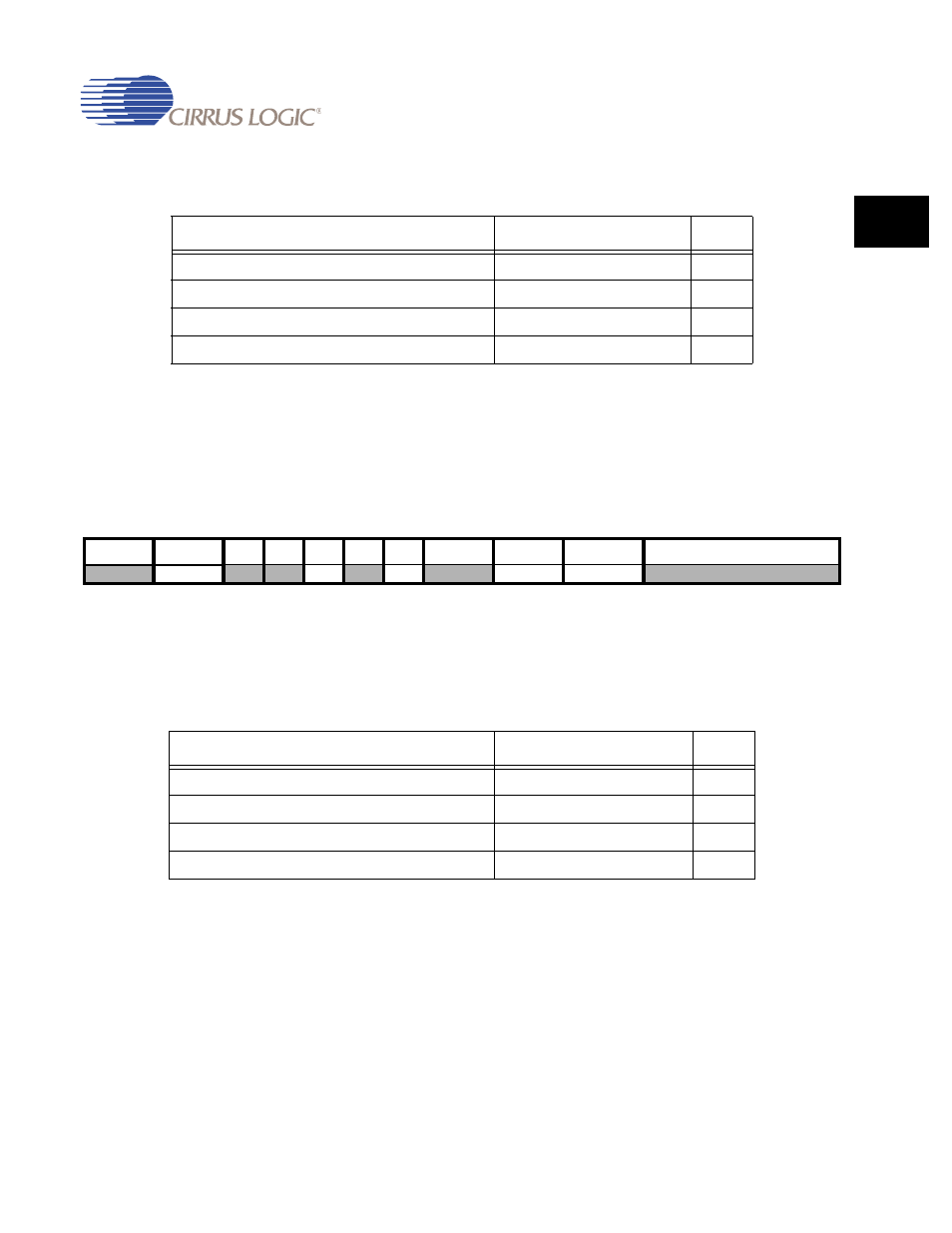

31:28

27:25

24

23

22

21

20

19:16

15:12

11:8

7:0

cond

1 1 0

P

U

N

W

0

Rn

CRd

0 1 0 1

8_bit_word_offset

Table 3-14. Mnemonic Codes for Storing Integer Values to Memory

Mnemonic

Addressing Mode

N

CFSTR32

Immediate pre-indexed

0

CFSTR32

Immediate post-indexed

0

CFSTR64

Immediate pre-indexed

1

CFSTR64

Immediate post-indexed

1