Cirrus Logic EP93xx User Manual

Page 77

DS785UM1

3-7

Copyright 2007 Cirrus Logic

MaverickCrunch Co-Processor

EP93xx User’s Guide

3

3

3

condition code field of any subsequent ARM instruction to gate the execution of that

instruction based on the result of a Crunch compare operation.

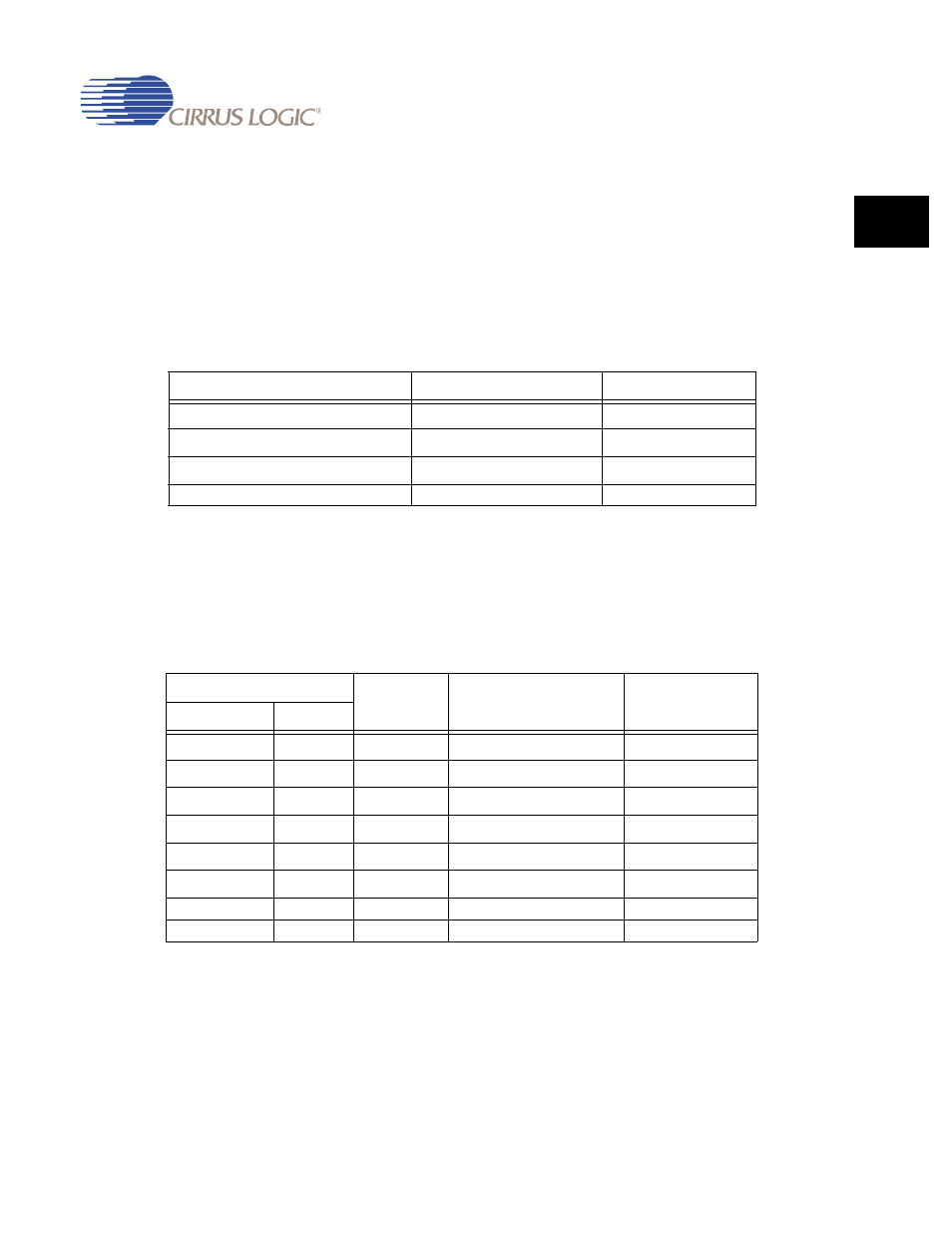

illustrates the legal relationships and, for each one, the values written to the FCC

bits and the NZCV flags. The FCC bits and the NZCV flags provide the same information, but

in different ways and in different places. Their values depend only on the relationship

between the operands, regardless of whether the operands are considered signed integer,

unsigned integer, or floating point. The unordered relationship can only apply to floating point

operands.

The NZCV flags are not computed exactly as with integer comparisons using the ARM CMP

instruction. Hence, when examining the result of Crunch comparisons, the condition codes

field of ARM instructions should be interpreted differently, as shown in

. The same

six condition codes should be used whether the comparison operands were signed integers,

unsigned integers, or floating point. No other condition codes are meaningful.

Table 3-3. Comparison Relationships and Their Results

Relationship

FCC[1:0]

NCZV

00

0100

01

1000

10

1001

Unordered

11

0000

Table 3-4. ARM

®

Condition Codes and Crunch Compare Results

Condition Code

Relationship

ARM Meaning

Crunch Meaning

Opcode[31:28] Mnemonic

0000

EQ

Equal

Equal

0001

NE

Not Equal

Not Equal

1010

GE

Signed Greater Than or Equal Greater Than or Equal

1011

LT

Signed Less Than

Less Than

1100

GT

Signed Greater Than

Greater Than

1101

LE

Signed Less Than or Equal

Less Than or Equal

1110

AL

N/A

Always (unconditional)

Always (unconditional)

1111

NV

N/A

Never

Never

A

B

=

A

B

<

A

B

>

A

B

=

A

B

≠

A

B

≥

A

B

<

A

B

>

A

B

≤