2 example: 24 bpp (packed) mode, 2 pixel end and start, 2 example: 24 bpp (packed) mode -9 – Cirrus Logic EP93xx User Manual

Page 273: 2 pixel end and start -9, Table 8-9. transfer example 2 -9, Table 8-10. transfer example 3 -9, Table 8-11. transfer example 4 -9, Table 8-12. transfer example 5 -9, Table 8-9

DS785UM1

8-9

Copyright 2007 Cirrus Logic

Graphics Accelerator

EP93xx User’s Guide

8

8

8

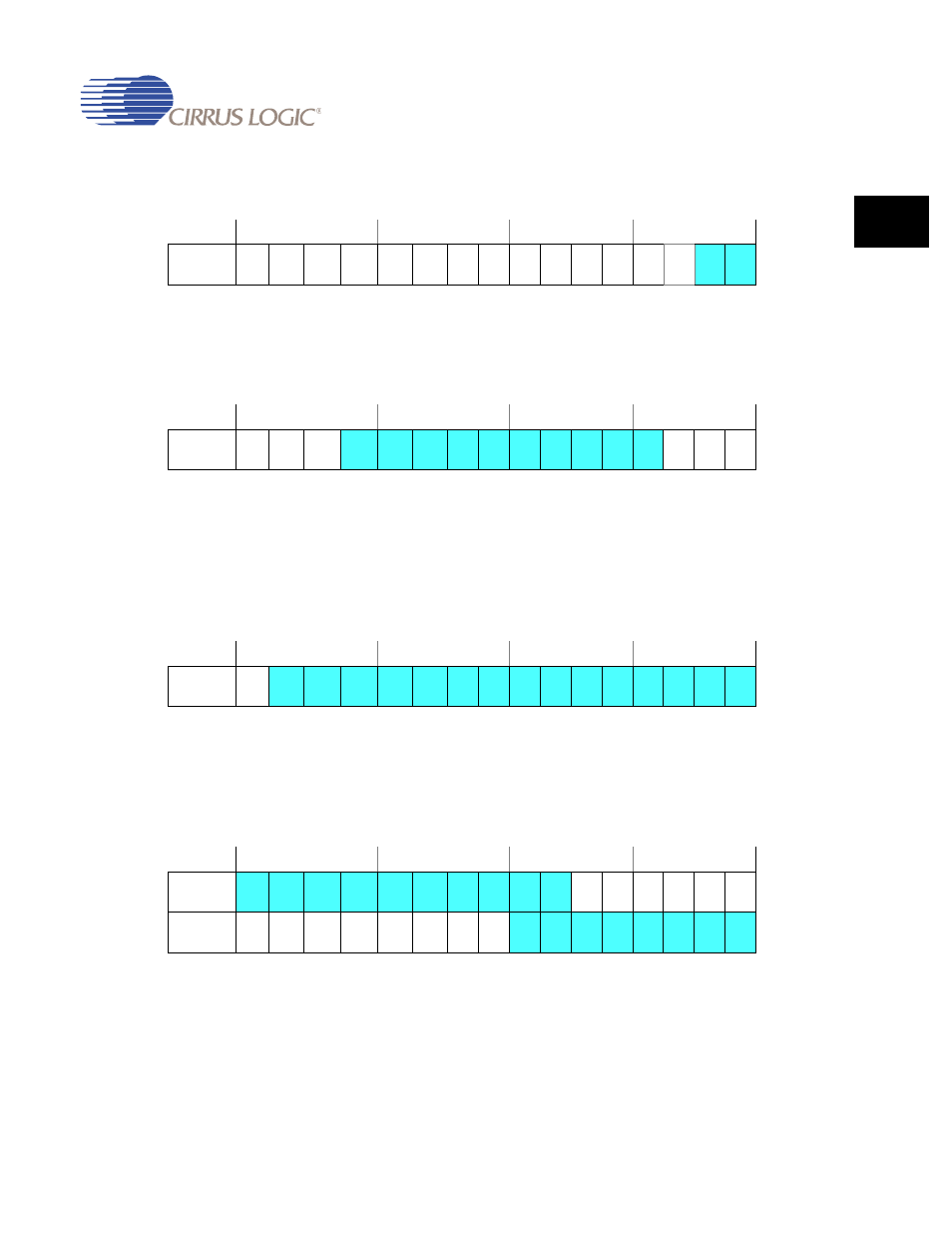

If a Block Copy starts at pixel 3 and 10 pixels are to be copied, the

register

would be loaded with 0x3 (4 words - 1 word = 0x3). The pixels fetched are highlighted in

.

8.5.1.2 Example: 24 BPP (packed) mode

If a Block Copy starts at pixel 0 and copies 5 pixels, the

register would be

filled with 0x3. This is because the first four pixels consume 3 words and the 5th pixel

consumes part of 1 word. This is a total of 4 words. So, the word width is 4 words - 1 word =

0x3. The pixels fetched are highlighted in

If a Block Copy starts at pixel 2 and copies 6 pixels, the

register would be

filled with 0x4. This is because the 1st pixel consumes part of the 1st word and the 4

remaining pixels consume the next 4 words. So, the word width is 5 words - 1 word = 0x4.

The pixels fetched are highlighted in

.

8.5.2 Pixel End and Start

Two registers are used to control where in a word the first and last pixels reside. This is

required since in all color depths more than 1 pixel can reside in a word of memory. This fact

requires that the programmer provide the hardware with the exact information of where in a

32-bit word a pixel starts or ends. One register,

, is used for the source

Table 8-9. Transfer Example 2

Address

31

0

31

0

31

0

31

0

0x0000 -

0x000C

FF

EE

DD

CC

BB

AA

99

88

77

66

55

44

33

22

11

00

Table 8-10. Transfer Example 3

Address

31

0

31

0

31

0

31

0

0x0000 -

0x000C

FF

EE

DD

CC

BB

AA

99

88

77

66

55

44

33

22

11

00

Table 8-11. Transfer Example 4

Address

31

0

31

0

31

0

31

0

0x0000 -

0x000C

55

44

44

44

33

33

33

22

22

22

11

11

11

00

00

00

Table 8-12. Transfer Example 5

Address

31

0

31

0

31

0

31

0

0x0000 -

0x000C

55

44

44

44

33

33

33

22

22

22

11

11

11

00

00

00

0x0010 -

0x001C

AA

AA

99

99

99

88

88

88

77

77

77

66

66

66

55

55