Table 2-6. cp15 arm920t register description -15 – Cirrus Logic EP93xx User Manual

Page 53

DS785UM1

2-15

Copyright 2007 Cirrus Logic

ARM920T Core and Advanced High-Speed Bus (AHB)

EP93xx User’s Guide

2

2

2

•

spsr: Saved Program Status Register contains CPSR after occurrence of an exception

CP15 has 16 registers that control the core as described in

.

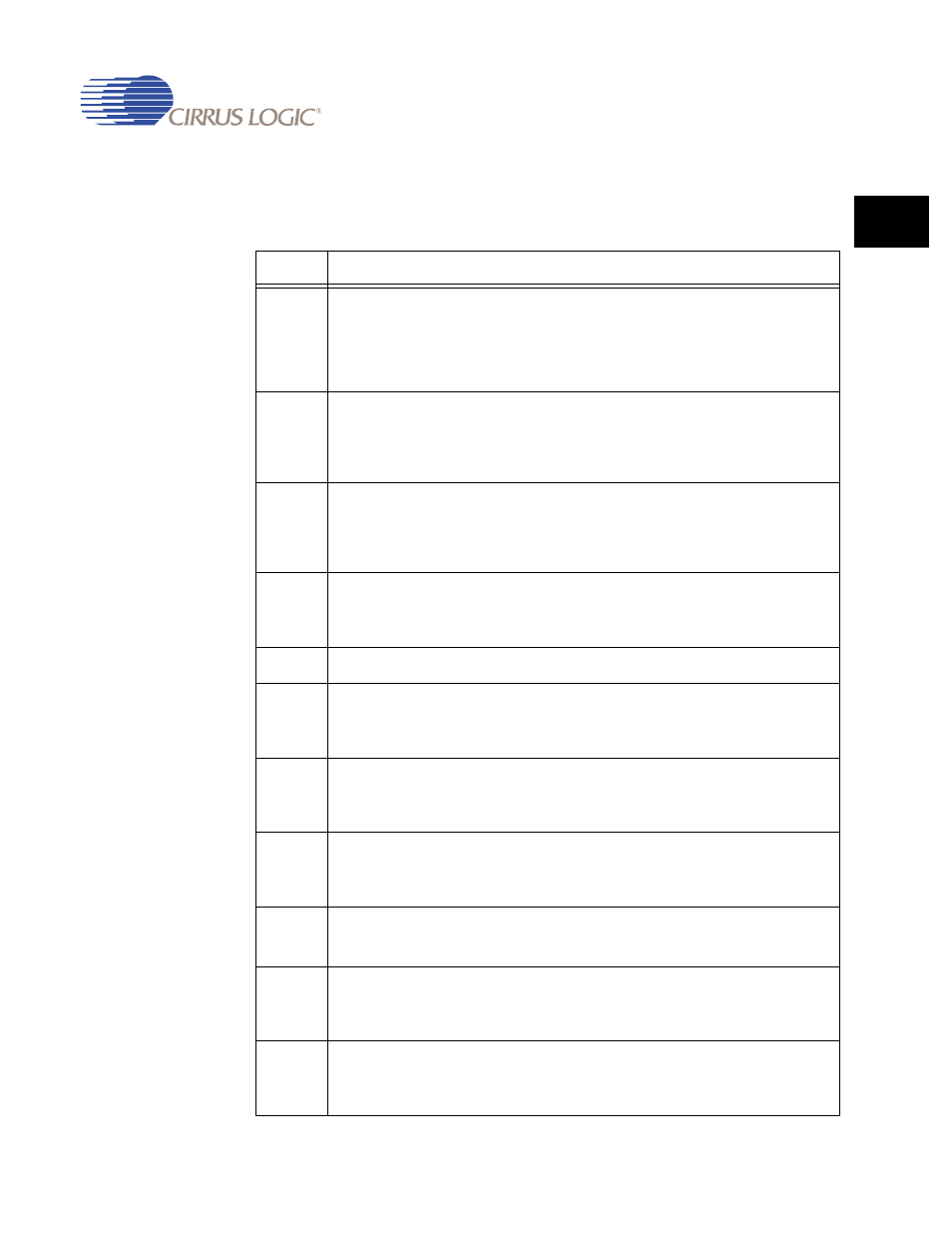

Table 2-6. CP15 ARM920T Register Description

Register

Description

0

ID Code:

(Read/Only) This register returns a 32-bit device ID code. ID Code data includes

the core type, revision, part number etc. Access to this register is via the instruction

MRC p15 0, Rd, c0, c0, 0.

Cache Code:

This register will return cache type, size and length of both I-Cache and D-

Cache, and associativity. Access to this register is via the instruction

MRC p15 0, Rd, c0, c0, 1.

1

Control Register:

(Read/Write) This register is used to enable: MMU, instruction and data

cache, round robin replacement ‘RR’-bit, system protection, ROM protection, and clocking

mode. Read/Write Instructions are:

MRC p15, 0, Rd, c1, c0, 0 - Read control register - value stored in Rd

MCR p15, 0, Rd, c1, c0, 0 - Write control register - value first loaded into Rd

2

Translation Base Table:

(Read/Write) This register contains the start address of the first

level translation table. The upper 18 bits represent the pointer to the table base. The lower

14 bits should be all zeroes for a write, unpredictable if read.

MRC p15, 0, Rd, c2, c0, 0 - Read TTB

MCR p15, 0, Rd, c2, c0, 0 - Write TTB

3

Domain Access Control:

(Read/Write) This register specifies permissions for each of the

16 domains. Read/Write Instructions are:

MRC p15, 0, Rd, c3, c0, 0

MCR p15, 0, Rd, c3, c0, 0

4

Reserved:

Do not access. Unpredictable behavior may result.

5

Fault Status:

(Read/Write) This register indicates the type of fault and the domain of the

most recent data abort. Read/Write Instructions are:

MRC p15, 0, Rd, c5, c0, 0 - read data FSR value

MCR p15, 0, Rd, c5, c0, 0 - write data FSR value

6

Fault Address:

(Read/Write) This register contains the address of the last data access

abort. Read/Write Instructions are:

MRC p15, 0, Rd, c6, c0, 0 - read FAR data

MCR p15, 0, Rd, c6, c0, 0 - write FAR data

7

Cache Operation:

(Write/Only) This register configures, or performs a clean (flush) of, the

cache and write buffer when written to. Example:

MRC p15, 0, Rd, c7, c7, 0 - Invalidate I/D-cache

MRC p15, 0, Rd, c7, c5, 0 - Invalidate I-Cache

8

TLB Operation:

(Write/Only) This register configures, or performs a clean (flush) of, the

TLB when written to. Example:

MRC p15, 0, Rd, c8, c7, 0 - Invalidate TLB

9

Cache Lockdown:

(Read/Write) This register prevents certain existing cache-lines from

being overwritten (locked) during a new cache-line fill. Examples:

MRC p15, 0, Rd, c9, c0, 1- Write lockdown base pointer for D-Cache

MRC p15, 0, Rd, c9, c0, 1 - Write lockdown base pointer for I-Cache

10

TLB Lockdown:

(Read/Write) This register prevents existing TLB entries from being

erased during a table walk. Examples:

MRC p15, 0, Rd, c10, c0, 1- Write lockdown base pointer for data TLB entry

MRC p15, 0, Rd, c10, c0, 1 - Write lockdown base pointer for instruction TLB entry