Cirrus Logic EP93xx User Manual

Page 621

DS785UM1

17-25

Copyright 2007 Cirrus Logic

IrDA

EP93xx User’s Guide

1

7

1

7

17

TXP:

Transmit Polarity Control.

0 - Encoded data is not inverted before being passed to

the pins.

1 - Encoded data is inverted before being passed to the

pins.

RXE:

Receive Enable.

0 - Ir receive logic is disabled and clocks are stopped.

1 - Ir receive logic is enabled.

TXE:

Transmit Enable.

0 - Transmit logic is disabled and clocks are stopped.

1 - Transmit logic is enabled.

TUS:

Transmit buffer Underrun Select.

0 - Transmit buffer underrun causes CRC, stop flag, and

SIP to be transmitted.

1 - Transmit buffer underrun causes an abort to be

transmitted.

BRD:

MIR Bit rate select.

0 - MIR data rate is 0.576 Mbit/s.

1 - MIR data rate is 1.152 Mbit/s.

0:

Must be written to “0”.

IrAdrMatchVal

Address:

0x808B_0008 - Read/Write

Default:

0x0000_0000

Definition:

IrDA Address Match Value Register contains the 8 bit address match value

field which is used by the receiver to selectively store only the data within the

receive frames which have the same address. For incoming frames which

have the same address value as the AMV field, the frame’s address, control

and data is stored in the receive buffer. For those that do not match, the

remainder of the frame is ignored and the receive logic searches for the

beginning of the next frame. This register is used for both MIR and FIR. The

AME bit in IrCtrl must be set to enable this function. Frames containing an

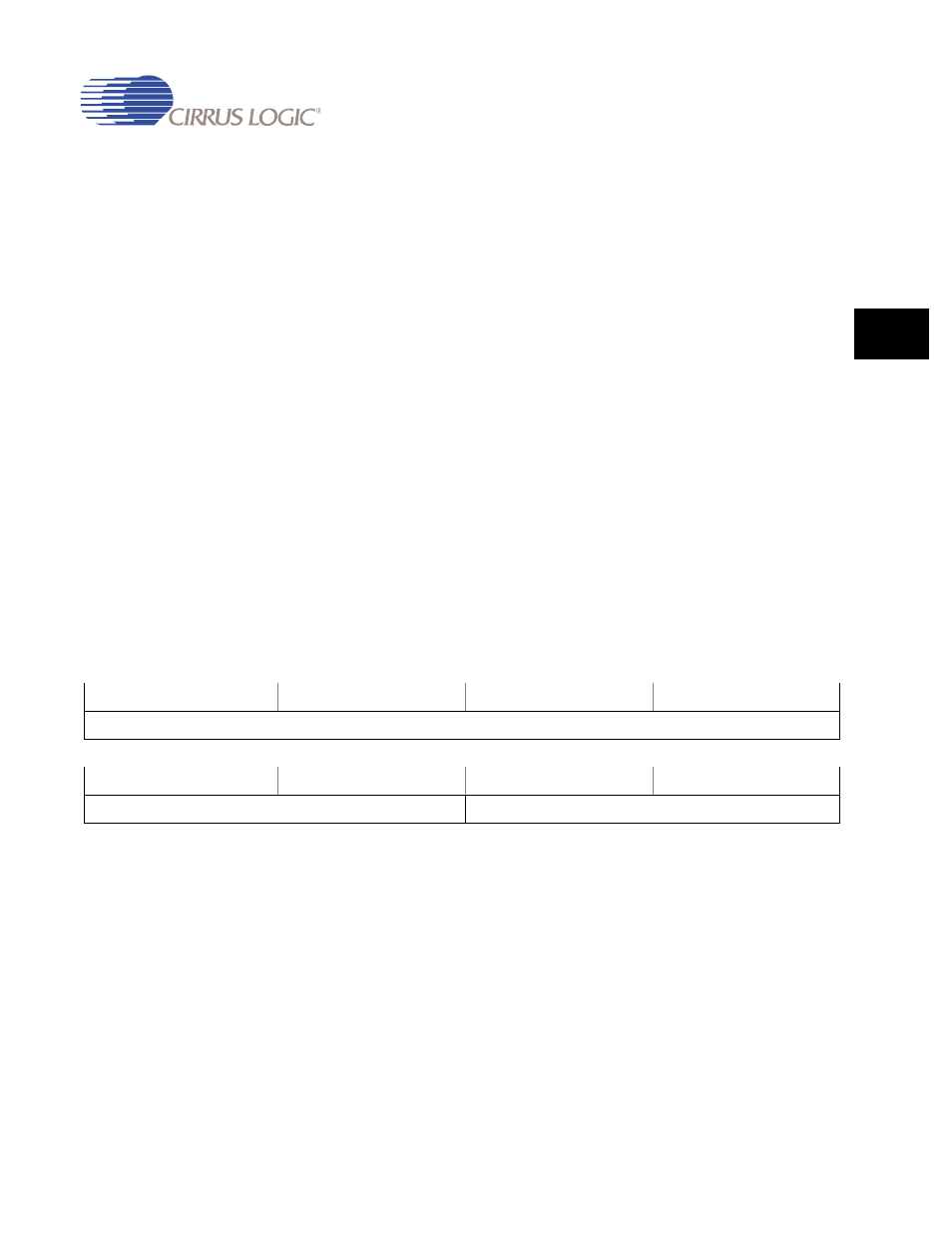

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

AMV