Table 2-5. register organization summary -14, Table 2-5 – Cirrus Logic EP93xx User Manual

Page 52

2-14

DS785UM1

Copyright 2007 Cirrus Logic

ARM920T Core and Advanced High-Speed Bus (AHB)

EP93xx User’s Guide

2

2

2

User mode in Thumb state limits access to the low registers r0-r7. To access to the high

registers, the ARM Core must first revert to the ARM state. The high registers are:

•

r0-r12: General purpose read/write 32-bit registers

•

r13 (sp): Stack Pointer

•

r14 (lr): Link Register

•

r15 (pc): Program Counter

•

cpsr: Current Program Status Register containing condition codes and operating modes

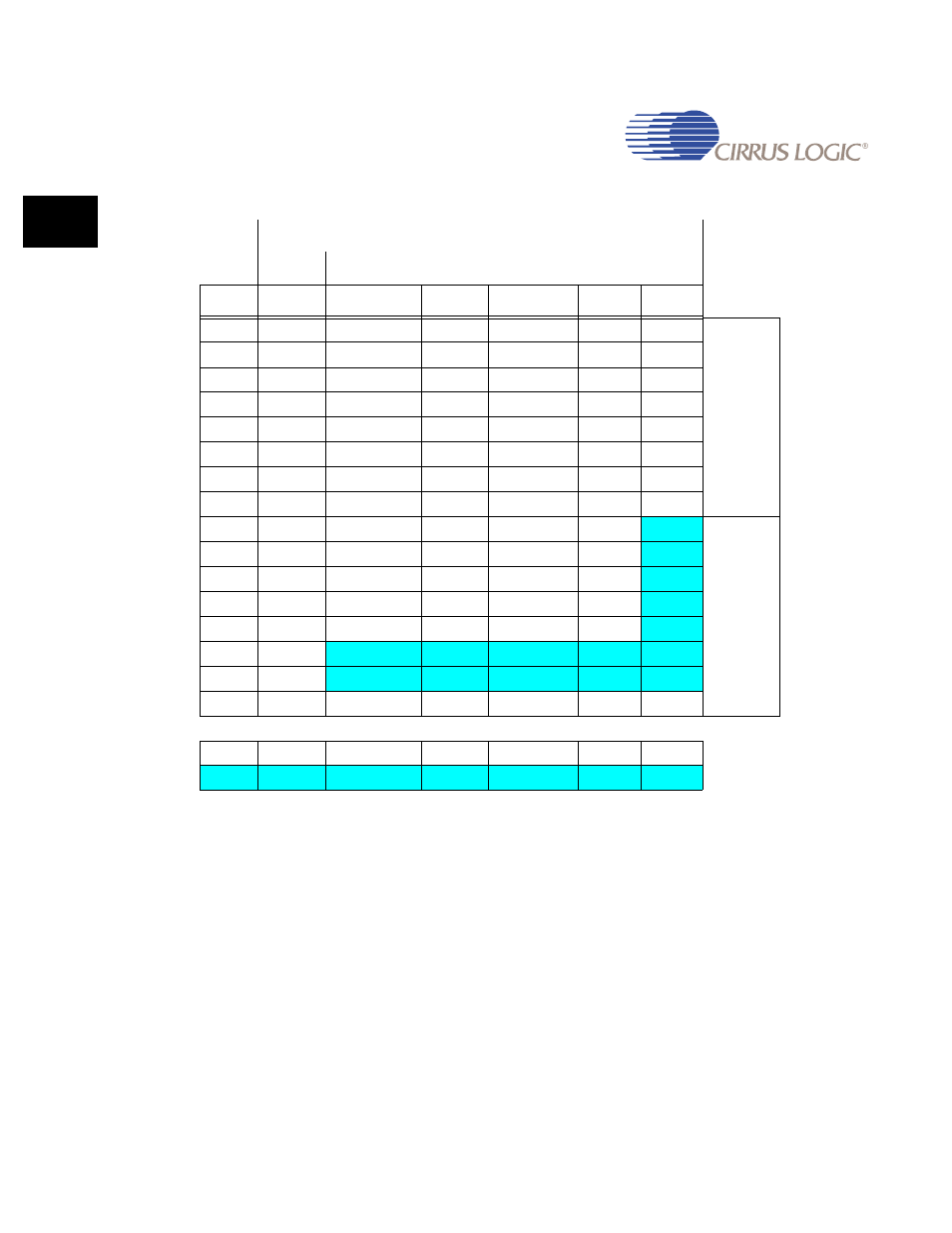

Table 2-5. Register Organization Summary

Privileged Modes

Exception Modes

User

System

Supervisor

Abort

Undefined

IRQ

FIQ

r0

r0

r0

r0

r0

r0

r0

Thumb

state low

registers

r1

r1

r1

r1

r1

r1

r1

r2

r2

r2

r2

r2

r2

r2

r3

r3

r3

r3

r3

r3

r3

r4

r4

r4

r4

r4

r4

r4

r5

r5

r5

r5

r5

r5

r5

r6

r6

r6

r6

r6

r6

r6

r7

r7

r7

r7

r7

r7

r7

r8

r8

r8

r8

r8

r8

r8_fiq

Thumb

state high

registers

r9

r9

r9

r9

r9

r9

r9_fiq

r10

r10

r10

r10

r10

r10

r10_fiq

r11

r11

r11

r11

r11

r11

r11_fiq

r12

r12

r12

r12

r12

r12

r12_fiq

r13(sp)

r13

r13_svc

r13_abt

r13_und

r13_irq

r13_fiq

r14(lr)

r14

r14_svc

r14_abt

r14_und

r14_irq

r14_fiq

r15(pc)

pc

pc

pc

pc

pc

pc

cpsr

cpsr

cpsr

cpsr

cpsr

cpsr

cpsr

spsr_svc

spsr_abt

spsr_und

spsr_irq

spsr_fiq

Note: Colored areas represent banked registers.