Bootsts – Cirrus Logic EP93xx User Manual

Page 517

DS785UM1

13-21

Copyright 2007 Cirrus Logic

SDRAM, SyncROM, and SyncFLASH Controller

EP93xx User’s Guide

1

3

1

3

13

Definition:

The Refresh Timer register is used to specify the period between refresh

cycles.

Bit Descriptions:

RSVD:

Reserved. - Unknown During Read

Refcnt:

Refresh Count - Read/Write

The value written to this field specifies, in multiples of the

period of HCLK, the time period between refresh cycles.

For example, if the period of HCLK is 20 ns, this field

should be written to 0x320 (decimal 800) to generate a

16 ms refresh period. On reset, this field defaults to

0x0080 (decimal 128) to generate a 2.56 ms refresh

period, but it must be written during the SDRAM

initialization routine to the appropriate value for the

SDRAM devices. If this field is written to 0x0000, no

refresh cycles are issued.

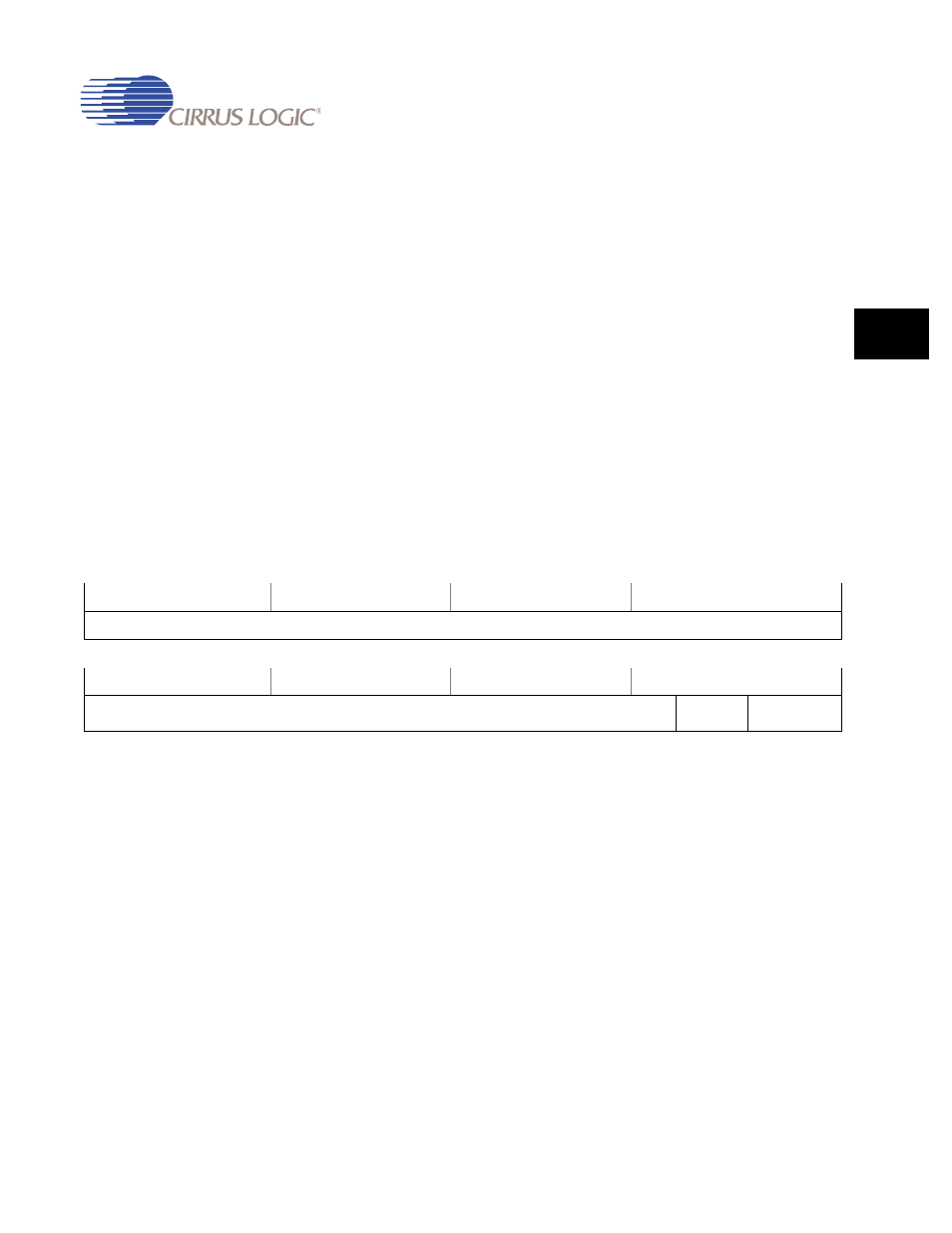

BootSts

Address: 0x8006_000C - Read Only

Default: 0x0000_0000

Definition:

When power on reset is asserted, the values of the boot mode option pins

shown in

are latched. The Boot Status register reflects those

latched values. This register can be read to determine which memory

configuration was used during the boot process.

Bit Descriptions:

RSVD:

Reserved - Unknown During Read

ASDO:

Latched ASDO pin value - Read Only

Boot Media:

1 - SyncROM or SyncFLASH

0 - Asynchronous ROM

Width:

Boot memory bus Width - Read Only

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

Latched

ASDO

Width