9 internal m2p/p2m dma functional description, 9 internal m2p/p2m dma functional description -7, Figure 10-1. dma m2p/p2m finite state machine -7 – Cirrus Logic EP93xx User Manual

Page 401

DS785UM1

10-7

Copyright 2007 Cirrus Logic

DMA Controller

EP93xx User’s Guide

1

0

1

0

10

The data received on each of the five peripheral receive DMA Rx Data buses is transferred

into an internal receive packer unit. The packer unit is used to convert the byte-wide data

received from the peripheral into words to be transferred over the system bus to the memory.

The packer unit stores 4 words (one quad-word) of data, which is the size of the burst

transfers to and from memory over the system bus. Provision for the memory access latency

is provided by FIFOs within the peripheral. The size of the FIFOs can be selected as

appropriate for the data rate generated by the peripheral.

Transmit data is fetched from system memory by the AHB master interface and placed into

the transmit un-packer. The transmit un-packer converts the quad-word burst of DMA data

into byte data for transmission over the transmit peripheral DMA bus. The transmit un-packer

contains 4 words (one quad-word) of storage. Additional latency is provided by FIFOs within

the peripheral, the size of which can be selected as appropriate for the peripheral.

The number of data transfers over the peripheral DMA bus (that is, the number of bytes) are

counted by packer/un-packer unit. If the number of bytes transferred reaches the

MaxTransfer count, the appropriate RxTC/TxTC signal is asserted causing the flush to

memory of data from a packer unit, and the invalidation of any data remaining in an un-

packer unit.

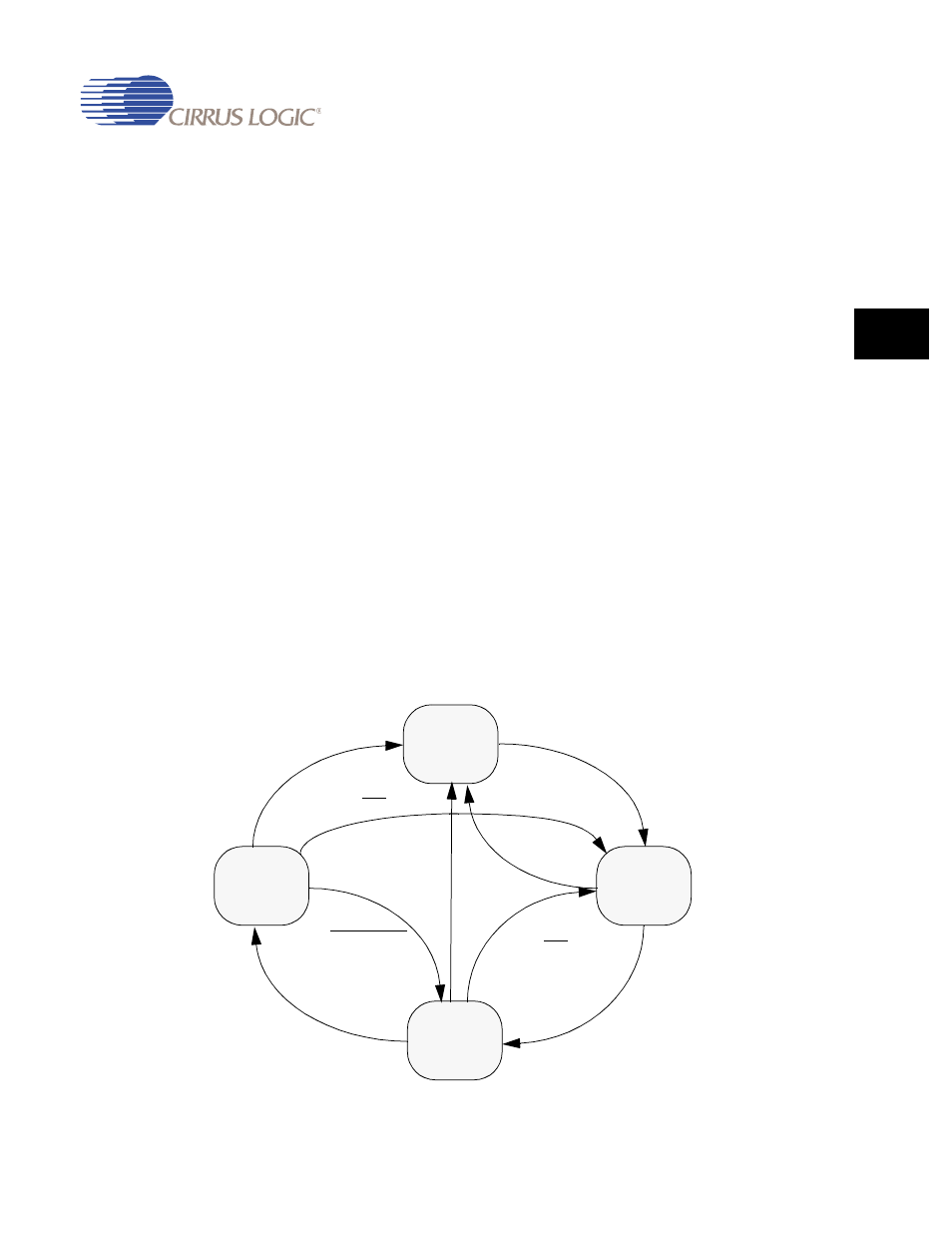

10.1.9 Internal M2P/P2M DMA Functional Description

10.1.9.1 Internal M2P/P2M DMA Buffer Control Finite State Machine

Each DMA internal M2P/P2M channel is controlled by a finite state machine (FSM) which

determines whether the channel is transferring data, and whether it is currently generating an

interrupt.

Figure 10-1. DMA M2P/P2M Finite State Machine

DMA_IDLE

DMA_STALL

DMA_ON

DMA_NEXT

DISABLE

ENABLE

DISABLE

Write Base

Address

Buffer End or

DISABLE

Buffer End or

Write

Base

Address

CE.ABORT.ICE

CE.ICE.ABORT

CE.ICE