1 load and store instructions, 1 load and store instructions -21 – Cirrus Logic EP93xx User Manual

Page 91

DS785UM1

3-21

Copyright 2007 Cirrus Logic

MaverickCrunch Co-Processor

EP93xx User’s Guide

3

3

3

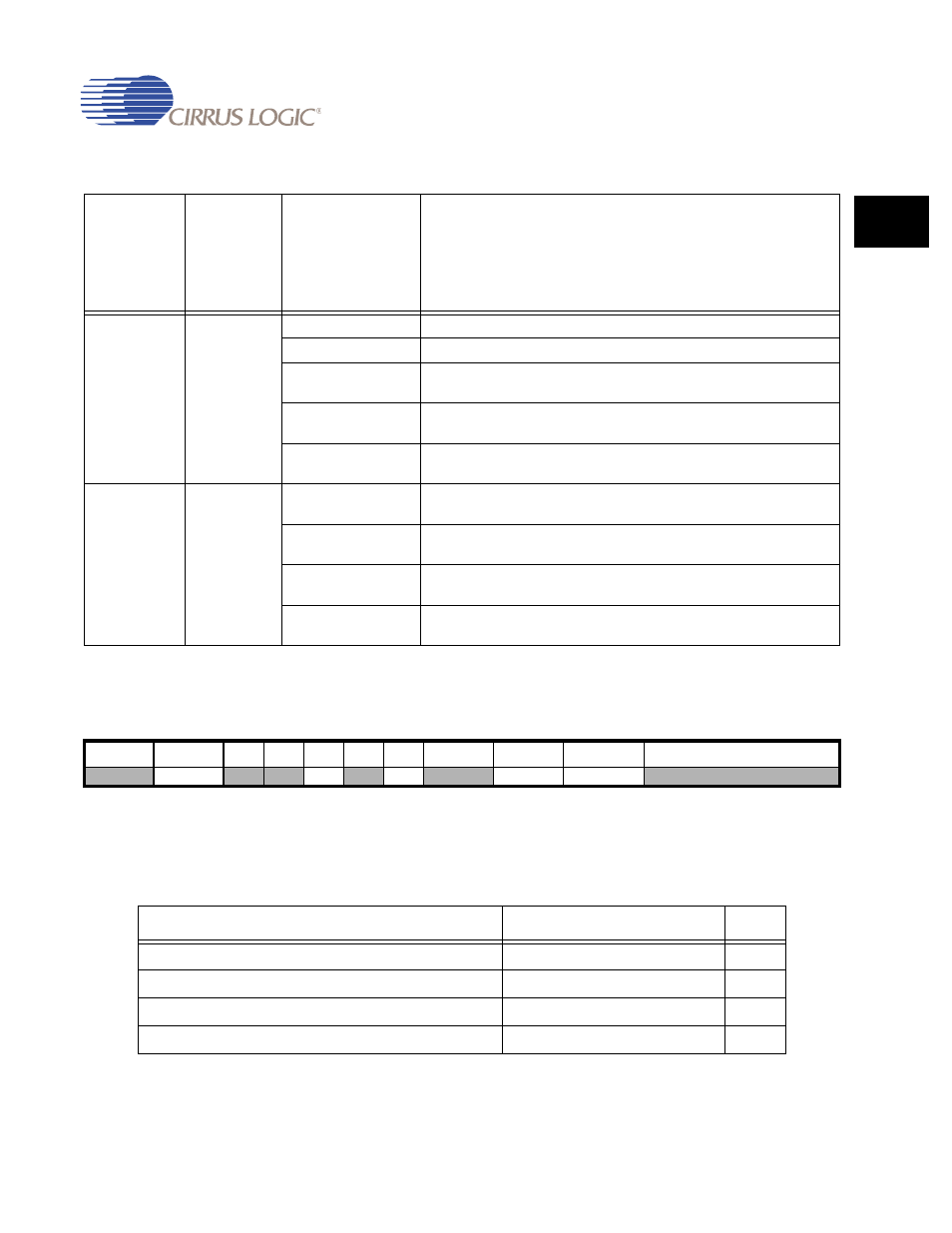

3.5.1 Load and Store Instructions

Loading Floating Point Value from Memory

Description:

Loads a single or double precision floating point value from memory into

MaverickCrunch register.

64-bit integer

arithmetic

CDP

cfabs64 CRd, CRn

CRd gets absolute value of CRn

cfneg64 CRd, CRn

CRd gets negation of CRn

cfadd64 CRd, CRn,

CRm

CRd gets sum of CRn and CRm

cfsub64 CRd, CRn,

CRm

CRd gets CRn minus CRm

cfmul64 CRd, CRn,

CRm

CRd gets the product of CRn and CRm

Accumulator

arithmetic

CDP

cfmadd32 CRa, CRd,

CRn, CRm

Accumulator CRa gets sum of CRd and the product of CRn and CRm

cfmsub32 CRa, CRd,

CRn, CRm

Accumulator CRa gets CRd minus the product of CRn and CRm

cfmadda32 CRa, CRd,

CRn, CRm

Accumulator CRa gets sum of accumulator CRd and the product of CRn

and CRm

cfmsuba32 CRa, CRd,

CRn, CRm

Accumulator CRa gets accumulator CRd minus the product of CRn and

CRm

31:28

27:25

24

23

22

21

20

19:16

15:12

11:8

7:0

cond

1 1 0

P

U

N

W

1

Rn

CRd

0 1 0 0

8_bit_word_offset

Table 3-11. Mnemonic Codes for Loading Floating Point Value from Memory

Mnemonic

Addressing Mode

N

CFLDRS

Immediate pre-indexed

0

CFLDRS

Immediate post-indexed

0

CFLDRD

Immediate pre-indexed

1

CFLDRD

Immediate post-indexed

1

Table 3-10. MaverickCrunch Instruction Set (Continued)

Maverick

Crunch

Co-

Processor

Instruction

Type

ARM

Co-

Processor

Instruction

Type

Instruction

Description