Cirrus Logic EP93xx User Manual

Page 554

14-32

DS785UM1

Copyright 2007 Cirrus Logic

UART1 With HDLC and Modem Control Signals

EP93xx User’s Guide

1

4

1

4

14

Definition:

HDLC Receive Information Buffer Register. This register is loaded when the

last data byte in a received frame is read from the receive FIFO. The CPU has

until the end of the next frame to read this register, or the RIL bit in the HDLC

Status Register is set.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

BPLLE:

Buffered Digital PLL Error.

1 - Receiver aborted last frame because DPLL lost the

carrier.

0 - Receiver did not abort because DPLL lost the carrier.

This bit is only valid when receiving Manchester-encoded

synchronous HDLC.

BC:

Received frame Byte Count.

The total number of valid bytes read from the RX FIFO

during the last HDLC frame.

BFRE:

Buffered Framing Error.

0 - No framing errors were encountered in the last frame.

1 - A framing error occurred during the last frame, causing

the remainder of the frame to be discarded.

BROR:

Buffered Receiver Over Run.

0 - The RX buffer did not overrun during the last frame.

1 - The receive FIFO did overrun during the last frame.

The remainder of the frame was discarded.

BCRE:

Buffered CRC Error.

0 - No CRC check errors occurred in the last frame.

1 - The CRC calculated on the incoming data did not

match the CRC value contained in the last frame.

BRAB:

Buffered Receiver Abort.

0 - No abort occurred in the last frame.

1 - The last frame was aborted.

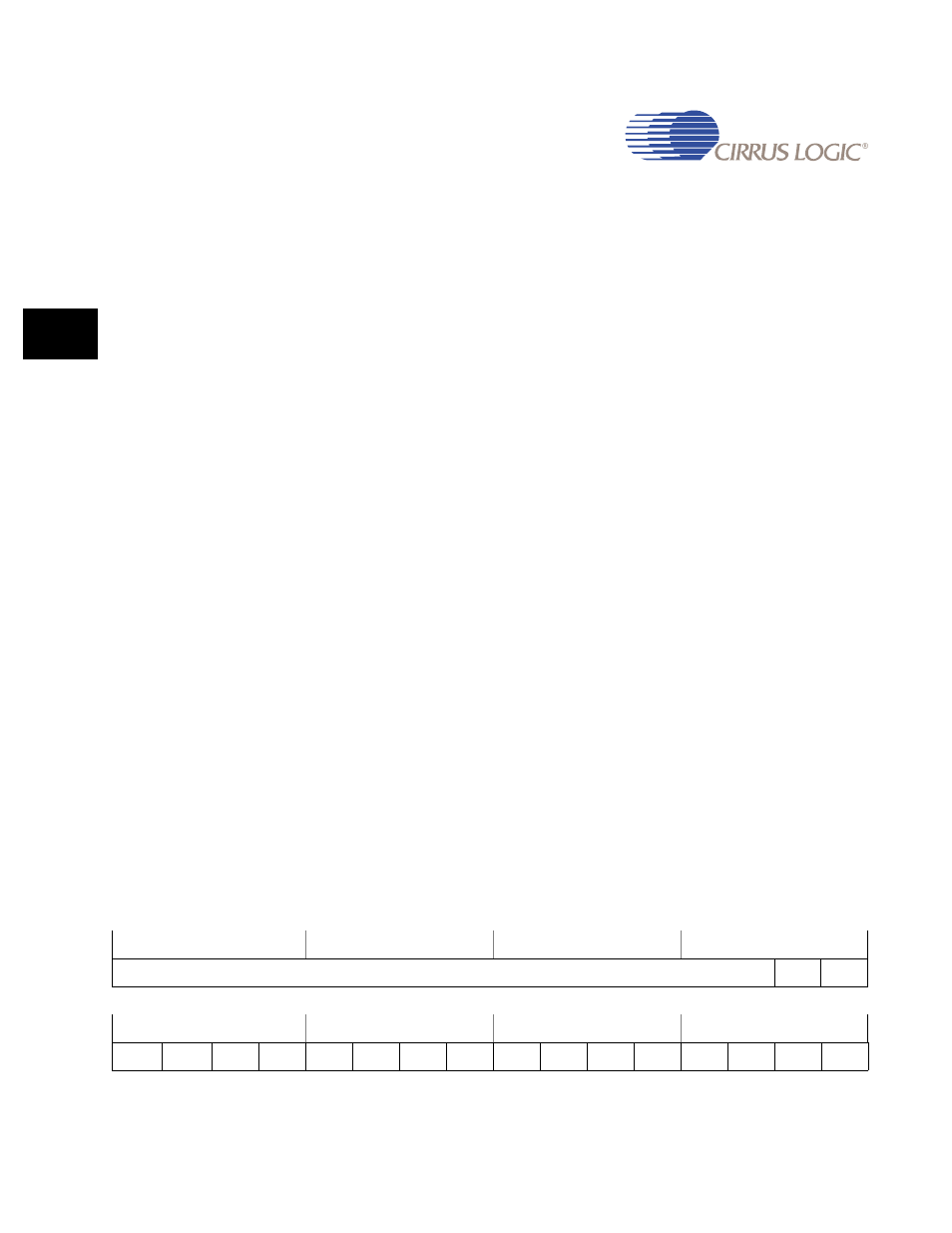

UART1HDLCSts

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

PLLE

PLLCC

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

LNKIDL

CRE

ROR

TBY

RIF

RSVD

RAB

RTO

EOF

RFL

RIL

RFC

RFS

TAB

TFC

TFS