2 clocking requirements, 3 bus bandwidth requirements, Table 16-2. devicecfg register bit functions -2 – Cirrus Logic EP93xx User Manual

Page 578

16-2

DS785UM1

Copyright 2007 Cirrus Logic

UART3 With HDLC Encoder

EP93xx User’s Guide

1

6

1

6

16

16.2.2 Clocking Requirements

There are two clocks, PCLK and UARTCLK.

UARTCLK frequency must accommodate the desired range of baud rates:

F

UARTCLK

(min) >= 32 x baud_rate(max)

F

UARTCLK

(max) <= 32 x 65536 x baud_rate(min)

The frequency of UARTCLK must also be within the required error limits for all baud rates to

be used.

To allow sufficient time to write the received data to the receive FIFO, UARTCLK must be less

than or equal to four times the frequency of PCLK:

F

UARTCLK

<= 4 x Fpclk

16.2.3 Bus Bandwidth Requirements

There are two basic ways of moving data to and from the UART FIFOs:

•

Direct DMA interface - this permits byte-wide access to the UART without using the

APB. The DMA block will pack or unpack individual bytes so that it reads or writes full

32-bit words rather than individual bytes.

•

Accessing the UART via the APB - this requires APB/AHB bus bandwidth. Then, both a

read and write are required for each 8-bit data byte.

Bandwidth requirements also depend on the selected baud rate, character size, parity

selection, number of stop bits, and spacing between characters (if receiving).

For example, assume 115,200 baud, 8-bit characters, even parity, one stop bit, no space

between characters. There are 11 bits per character, so 115,200 / 11 = 10,473 characters per

second. If both transmitting and receiving, 20,945 characters per second pass through the

UART. Accessing the UART through the DMA interface requires one access per 32-bits,

implying only 20,945 / 4 = 5,236 AHB accesses per second. Accessing the UART through the

APB requires two accesses per byte, implying 20,945 APB buss accesses.

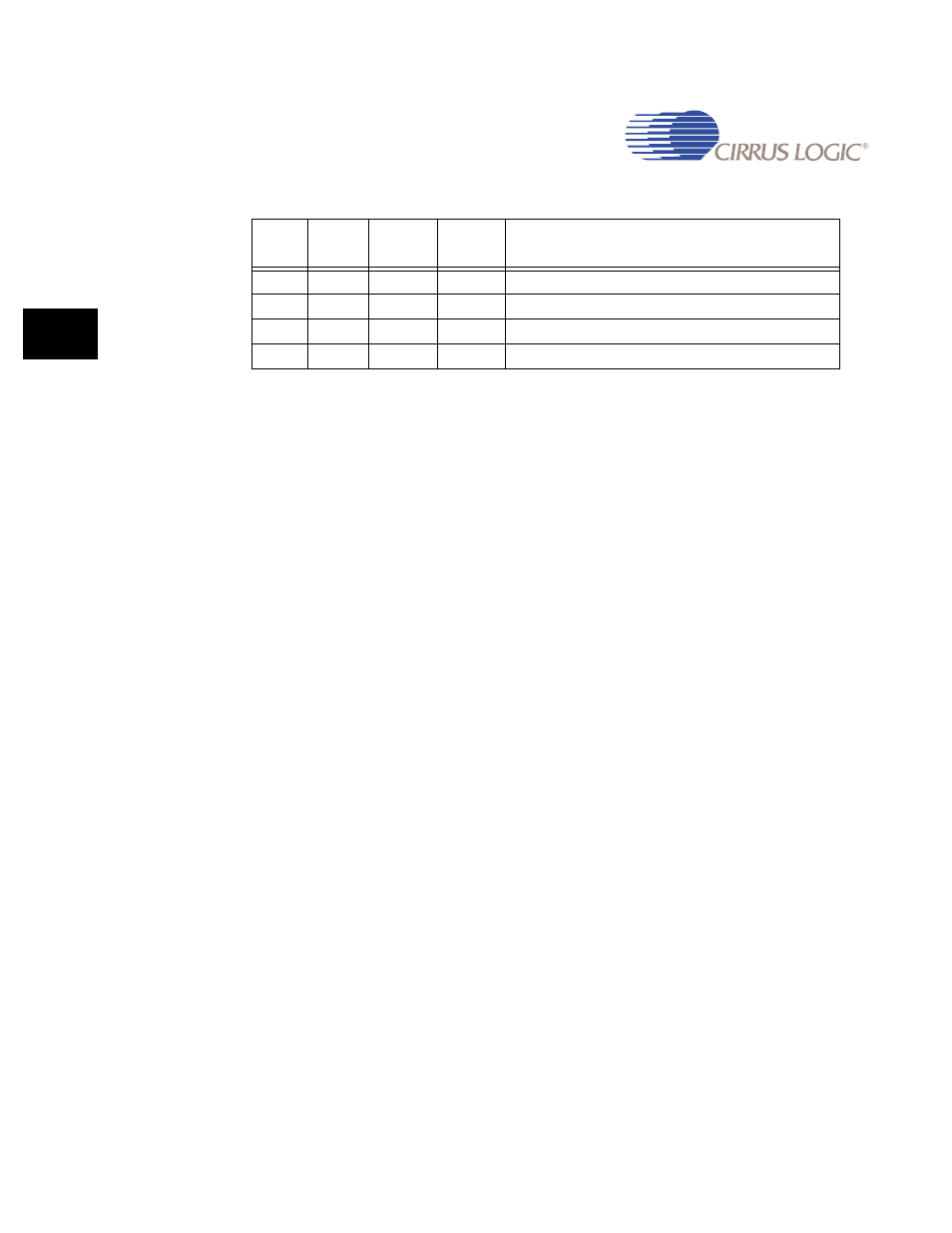

Table 16-2. DeviceCfg Register Bit Functions

bit 26

TonG

bit 15

HC3IN

bit 14

HC3EN

bit 12

HC1EN

Function

x

x

0

x

External HDLC clock input is driven low.

x

0

1

0

External HDLC clock input is driven by EGPIO[3].

x

1

1

0

Internal HDLC clock output drives EGPIO[3].

1

0

0

0

TENn output drives EGPIO[3].