Cirrus Logic EP93xx User Manual

Page 89

DS785UM1

3-19

Copyright 2007 Cirrus Logic

MaverickCrunch Co-Processor

EP93xx User’s Guide

3

3

3

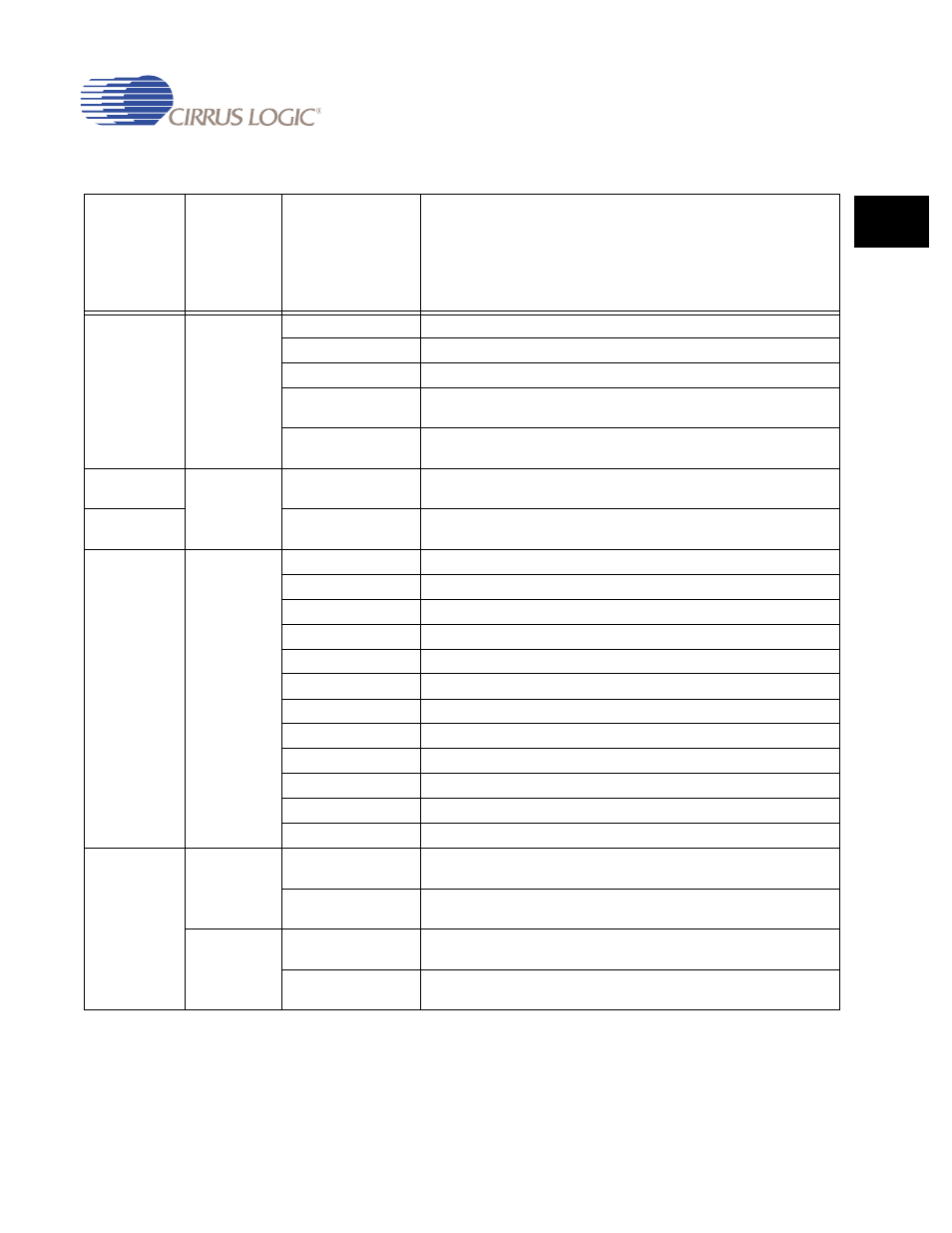

Moves from

accumulator

CDP

cfmv32al CRd, CRn

Move accumulator CRn[31:0] to 32-bit integer CRd[31:0]

cfmv32am CRd, CRn

Move accumulator CRn[63:32] to 32-bit integer CRd[31:0]

cfmv32ah CRd, CRn

Move accumulator CRn[71:64] to lower 8 bits of 32-bit integer CRd[31:0]

cfmv32a CRd, CRn

Saturate to 32-bit integer and move accumulator CRn[31:0] to 32-bit

integer CRd[31:0]

cfmv64a CRd, CRn

Saturate to 64-bit integer and move accumulator CRn[63:0] to 64-bit

integer CRd

Move to

DSPSC

CDP

cfmvsc32 CRd, CRn

Move CRd to DSPSC; CRn is ignored

Move from

DSPSC

cfmv32sc CRd, CRn

Moves DSPSC to CRd; CRn is ignored

Conversions

and copies

CDP

cfcpys CRd, CRn

Copy a single from CRn to CRd

cfcpyd CRd, CRn

Copy a double from CRn to CRd

cfcvtsd CRd, CRn

Convert a single in CRn to a double in CRd

cfcvtds CRd, CRn

Convert a double in CRn to a single in CRd

cfcvt32s CRd, CRn

Convert a 32-bit integer in CRn to a single in CRd

cfcvt32d CRd, CRn

Convert a 32-bit integer in CRn to a double in CRd

cfcvt64s CRd, CRn

Convert a 64-bit integer in CRn to a single in CRd

cfcvt64d CRd, CRn

Convert a 64-bit integer in CRn to a double in CRd

cfcvts32 CRd, CRn

Convert a single in CRn to a 32-bit integer in CRd

cfcvtd32 CRd, CRn

Convert a double in CRn to a 32-bit integer in CRd

cftruncs32 CRd, CRn

Truncate a single in CRn to a 32-bit integer in CRd

cftruncd32 CRd, CRn

Truncate a double in CRn to a 32-bit integer in CRd

Shifts

MCR

cfrshl32 CRm, CRn,

Rd

Shift 32-bit integer in CRn by two’s complement value in Rd and store in

CRm

cfrshl64 CRm, CRn,

Rd

Shift 64-bit integer in CRn by two’s complement value in Rd and store in

CRm

CDP

cfsh32 CRd, CRn,

Shift 32-bit integer in CRn by

is between -32 and 31, inclusive

cfsh64 CRd, CRn,

Shift 64-bit integer in CRn by

is between -32 and 31, inclusive

Table 3-10. MaverickCrunch Instruction Set (Continued)

Maverick

Crunch

Co-

Processor

Instruction

Type

ARM

Co-

Processor

Instruction

Type

Instruction

Description