Blinkrate, Blinkmask, Blink control registers blinkrate – Cirrus Logic EP93xx User Manual

Page 245

DS785UM1

7-63

Copyright 2007 Cirrus Logic

Raster Engine With Analog/LCD Integrated Timing and Interface

EP93xx User’s Guide

7

7

7

Blink Control Registers

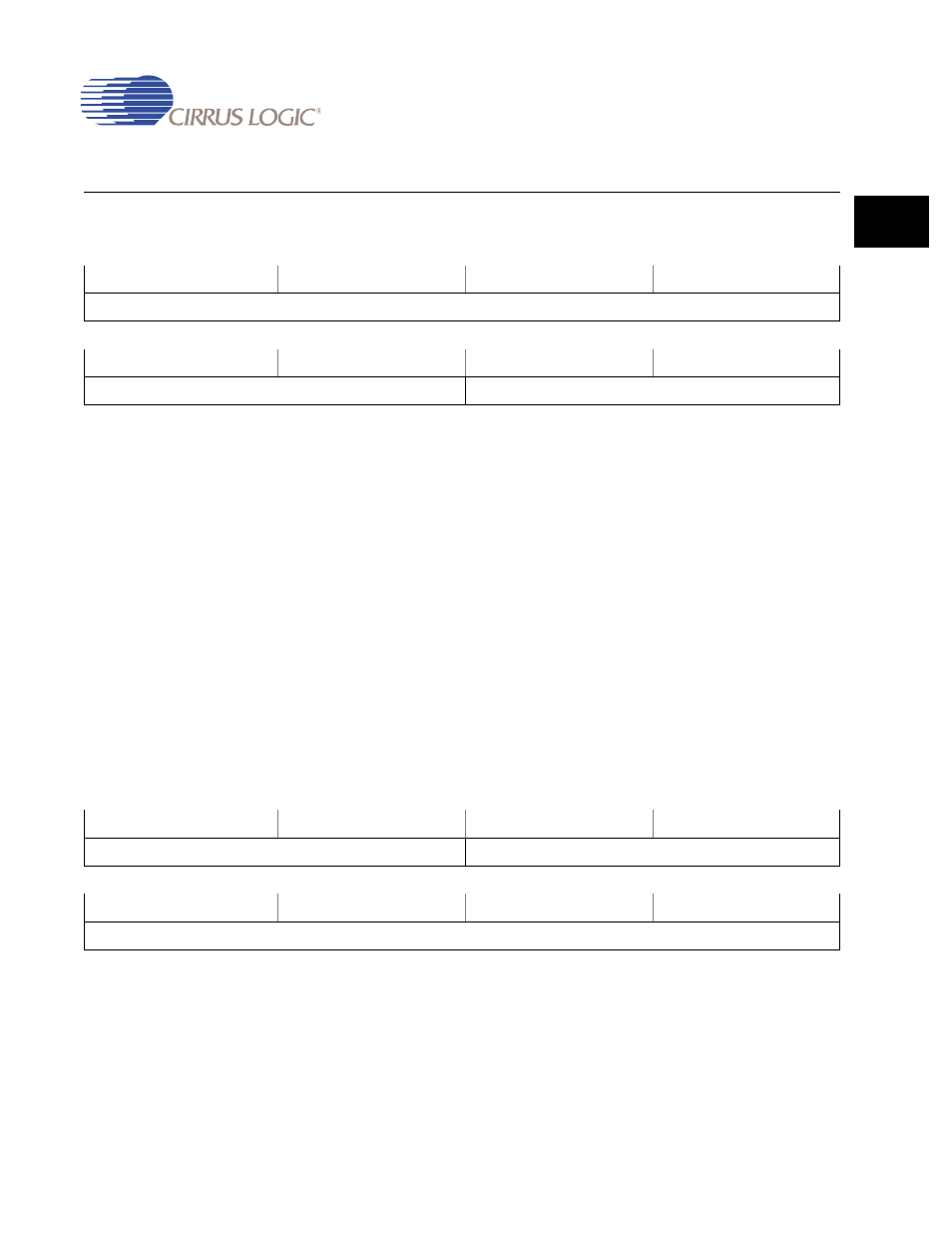

BlinkRate

Address: 0x8003_0040

Default: 0x0000_0000

Definition: Blink Rate Control register

Bit Descriptions:

RSVD:

Reserved - Unknown during read

RATE:

Rate - Read/Write

The blink rate value that is written to this field controls the

number of video frames that occur before the LUT

addresses assigned to ‘blink’ change between masked

and unmasked (see

on/off blink cycle is controlled by this equation:

Blink Cycle = 2 x (1/VCLK) x HClkTotal x VLinesTotal x

(255 - BlinkRate)

BlinkMask

Address: 0x8003_0044

Default: 0x0000_0000

Definition: Blink Mask register

This register is used in conjunction with the

register to determine

which pixels that are fetched from SDRAM are blink pixels.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

RATE

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

MASK

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

MASK