Table 8-21. words needed for six 24-bit pixels -19 – Cirrus Logic EP93xx User Manual

Page 283

DS785UM1

8-19

Copyright 2007 Cirrus Logic

Graphics Accelerator

EP93xx User’s Guide

8

8

8

comprise the first scan line of the source image.

shows that six 32-bit words are needed to contain six 24-

bit pixels. So, LEN = 6 - 1 = 5 = 0x5.

2. Setup Destination Memory

A. Write the desired values to the SPEL field and the EPEL field in the

register.

SPEL is the starting pixel position within the word that the pixel-copy will begin with.

EPEL is the ending pixel position within the word that the pixel-copy will end with.

See

For example, if the image is to be copied to position (81, 105) and the pixel depth is

16-bits, the value for SPEL is (81 x 16)% 32 = 16 = 0x10 and the value for EPEL is

(105 x 16)% 32 = 16 = 0x10

B. Write the word-aligned value of the SDRAM address ‘for the beginning of the copy

destination’ to the

register.

C. Write the line length value to the LEN field in the

register,

where LEN is determined by:

(1).Find how many pixels occupy a 32-bit word. For example, four 8-bit pixels can

occupy a 32-bit word.

(2).Find the width of the display in pixels. For example, a 640x480 display has a

width of 640 pixels.

(3).The line length, LEN, is determined by the stride of the display, that is, how

many 32-bit words are needed to populate the width of the display with pixels.

From steps 1 and 2, the stride for this example is 640 pixels divided by 4,

where 4 is the number of 8-bit pixels that occupy a word. So, for this example,

line length is 640 divided by 4 = 160 = 0xA0.

Usually the same LEN value is used in both the

register

register.

D. Write the value of the WIDTH field to the

register, where WIDTH

specifies the number of 32-bit words, minus 1, that are needed to contain the pixels

that comprise the 1st scan line of the destination image. For an example, please

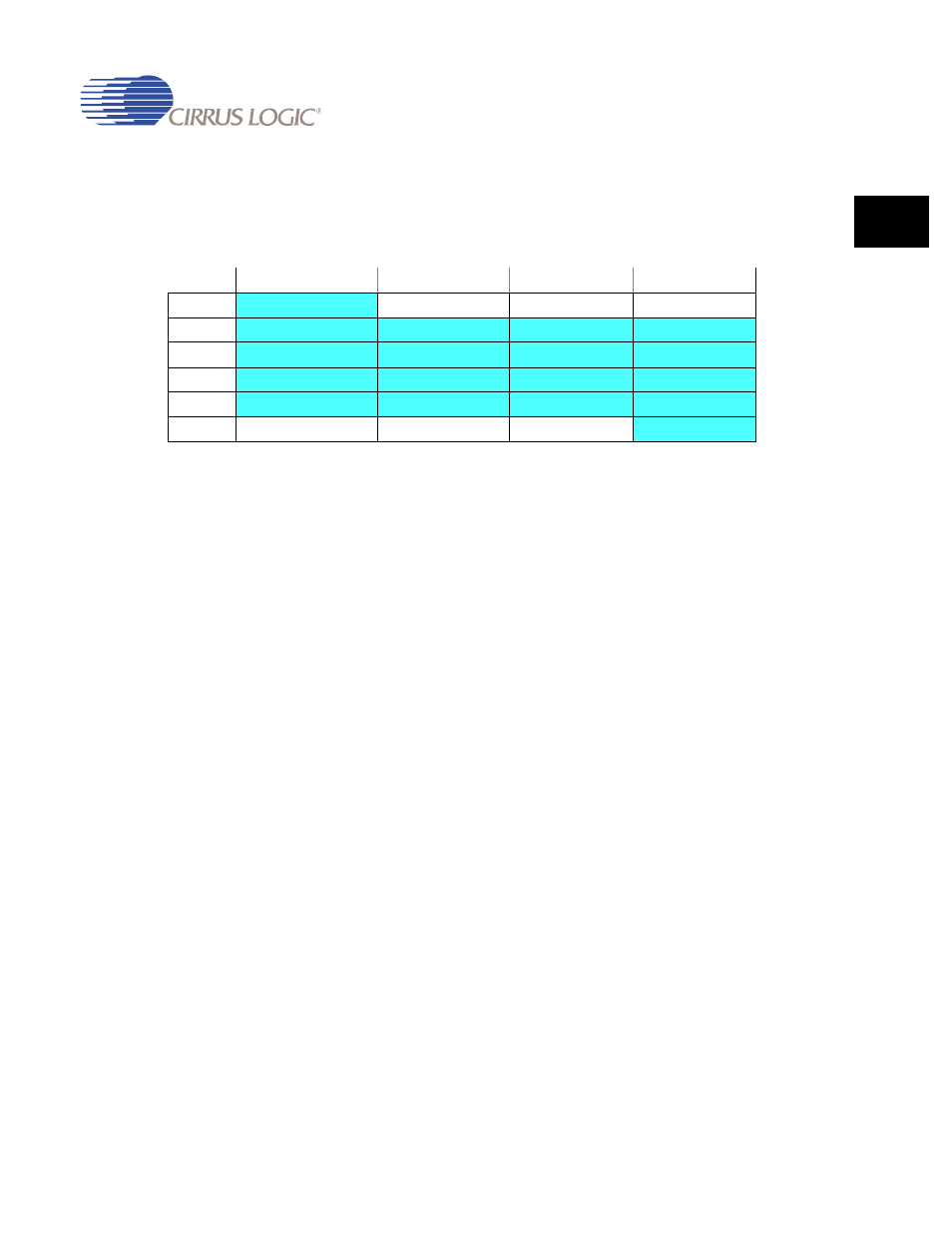

Table 8-21. Words Needed for Six 24-Bit Pixels

Address

31

24

23

16

15

8

7

0

0x0000

P1

P0

P0

P0

0x0004

P2

P2

P1

P1

0x0008

P3

P3

P3

P2

0x000C

P5

P4

P4

P4

0x0010

P6

P6

P5

P5

0x0014

P7

P7

P7

P6