4 irda integration information, 1 enabling infrared modes, 2 clocking requirements – Cirrus Logic EP93xx User Manual

Page 617: 4 irda integration information -21, Table 17-5. uart2 / irda modes -21

DS785UM1

17-21

Copyright 2007 Cirrus Logic

IrDA

EP93xx User’s Guide

1

7

1

7

17

17.5.4 IrDA Integration Information

17.5.4.1 Enabling Infrared Modes

17.5.4.2 Clocking Requirements

There are four clocks, PCLK, MIRCLK, FIRCLK, and UARTCLK.

Version 1.1 of the Infrared Data Association standard indicates the following:

•

FIRCLK must by 48.0 MHz with a tolerance of 0.01%.

•

MIRCLK must be 18.432 MHz with a tolerance of 0.1%.

The worst case ratio that can be supported for PCLK:FIRCLK is a ratio of 1:5. The maximum

that PCLK can be is 66 MHz, therefore:

Any frequencies outside the above range are not supported and will result in incorrect

behavior of the FIR mode of the infrared peripheral.

Since MIRCLK is 18.432 MHz, PCLK can be as low as 3.68 MHz and as high as 66 MHz. Any

PCLK frequency in this range is allowable. Any PCLK frequencies outside the range are not

supported and will result in incorrect behavior of the MIR mode of the infrared peripheral,

therefore:

The tolerance of UARTCLK is defined by the UART to which it is connected.

UARTCLK frequency must accommodate the desired range of baud rates:

The frequency of UARTCLK must also be within the required error limits for all baud rates to

be used.

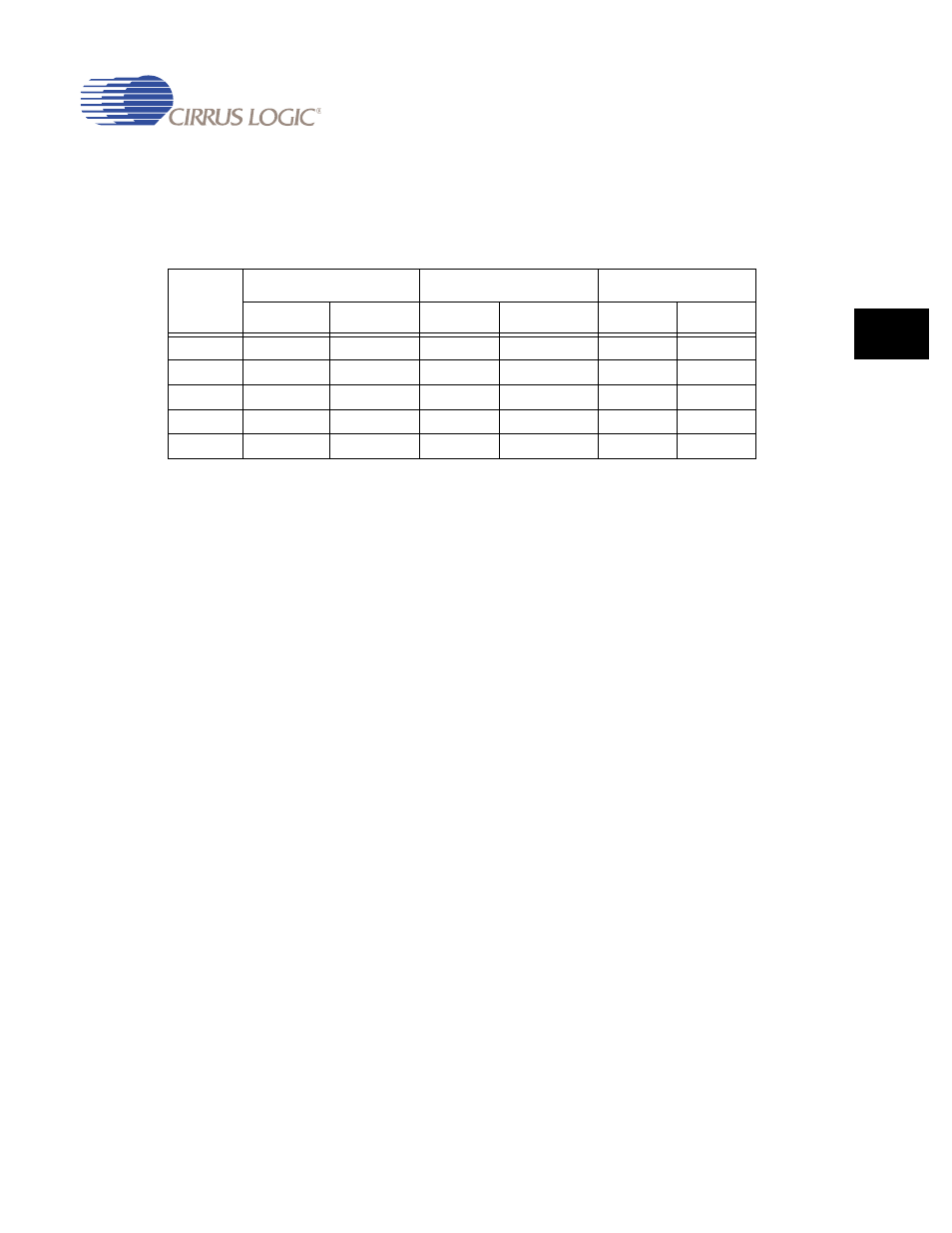

Table 17-5. UART2 / IrDA Modes

Mode

DeviceCfg Register

UART2Ctrl Register

IrEnable Register

U2EN

IonU2

SIREn

UARTE

EN[1]

EN[0]

Disabled

0

x

0

0

0

0

UART2

1

0

0

1

0

0

SIR

1

1

1

1

0

1

MIR

x

1

0

0

1

0

FIR

x

1

0

0

1

1

1

5

---F

FIRCLK

F

PCLK

66.0MHz

<

<

3.68MHz

F

PCLK

66.0MHz

≤

≤

F

UARTCLK

MIN

32

baudrate

MAX

×

≥

F

UARTCLK

MA X

32

65536

b

×

audrate

MIN

Ч

≤