Cirrus Logic EP93xx User Manual

Page 455

DS785UM1

11-15

Copyright 2007 Cirrus Logic

Universal Serial Bus Host Controller

EP93xx User’s Guide

1

1

1

1

11

RWE: RemoteWakeupEnable:

This bit is used by HCD to enable or disable the remote

wakeup feature upon the detection of upstream resume

signaling. When this bit is set and the ResumeDetected bit

in HcInterruptStatus is set, a remote wakeup is signaled to

the host system. Setting this bit has no impact on the

generation of hardware interrupt.

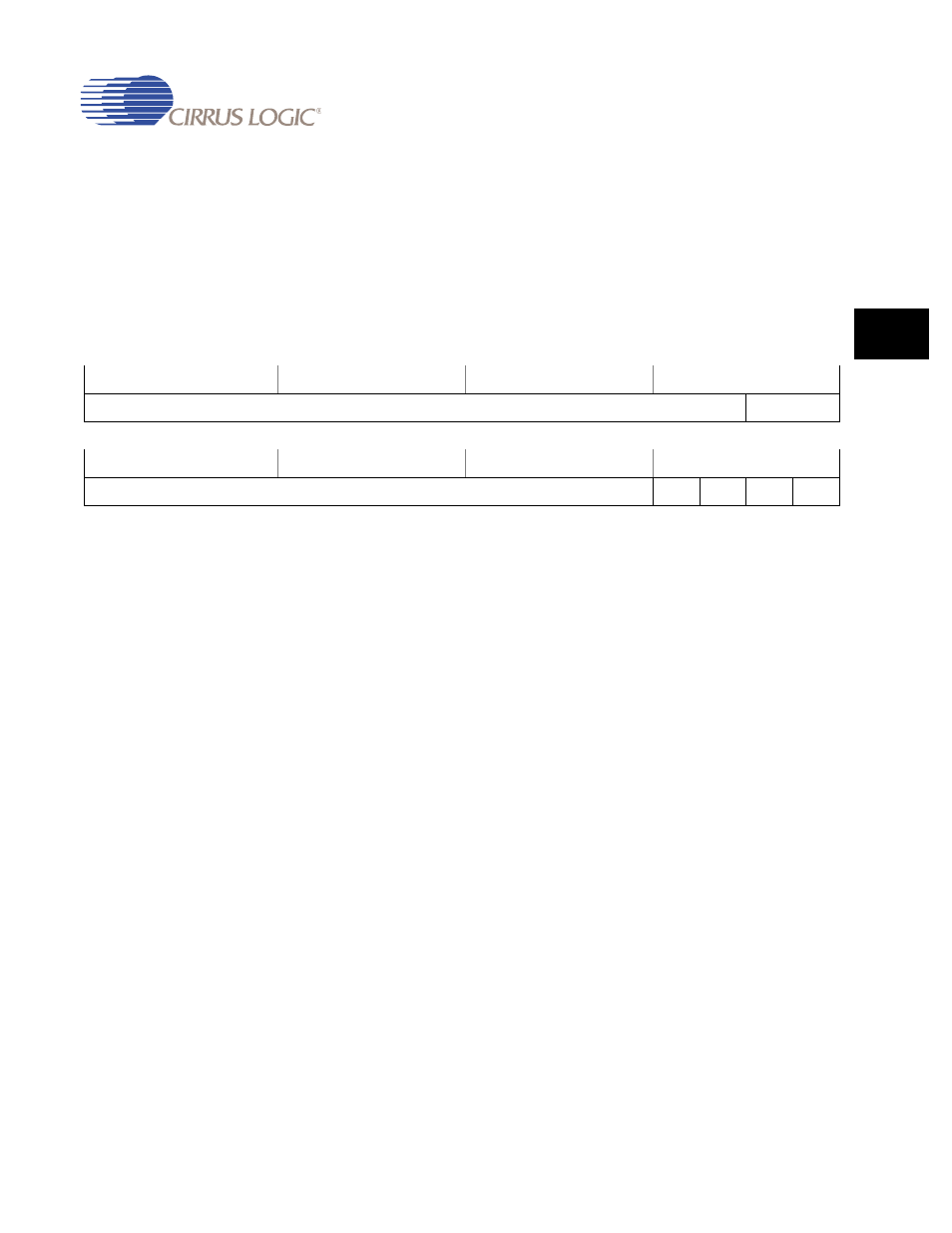

HcCommandStatus

Address:

0x8002_0008

Default:

0x0000_0000

Definition:

Provides current controller status and accepts controller commands.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

HCR: HostControllerReset:

This bit is set by HCD to initiate a software reset of HC.

Regardless of the functional state of HC, it moves to the

USBSUSPEND state in which most of the operational

registers are reset except those stated otherwise; e.g., the

InterruptRouting field of HcControl, and no Host bus

accesses are allowed. This bit is cleared by HC upon the

completion of the reset operation. The reset operation

must be completed within 10 ms. This bit, when set,

should not cause a reset to the Root Hub and no

subsequent reset signaling should be asserted to its

downstream ports.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

SOC

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

OCR

BLF

CLF

HCR