Parllifin – Cirrus Logic EP93xx User Manual

Page 243

DS785UM1

7-61

Copyright 2007 Cirrus Logic

Raster Engine With Analog/LCD Integrated Timing and Interface

EP93xx User’s Guide

7

7

7

P3 --> D3

P[2:0] --> D[2:0]

SPCLK --> E

Smart Panel R/W and RS signals must be implemented

via GPIOs and controlled via software.

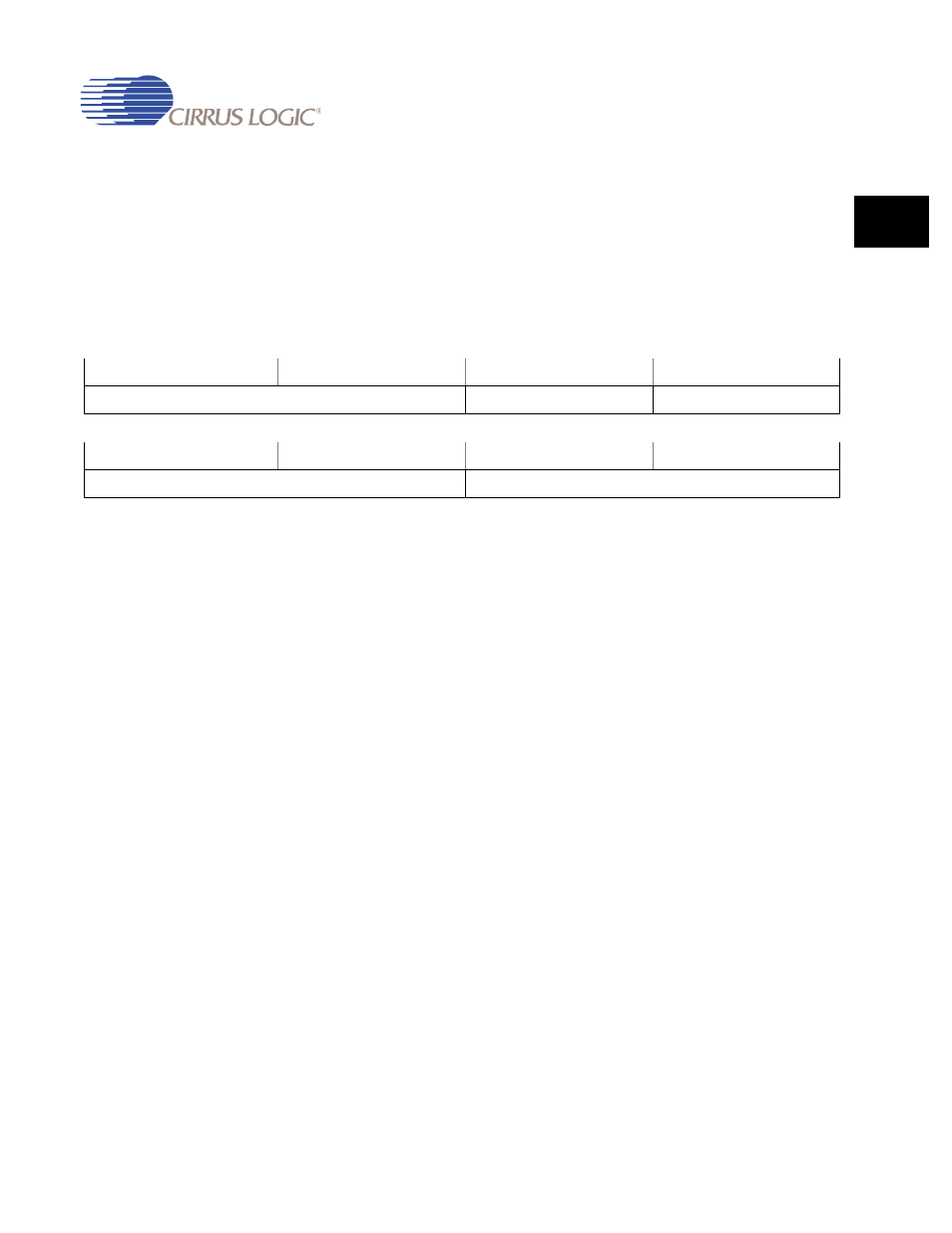

ParllIfIn

Address: 0x8003_005C

Default: 0x0000_0000

Definition: Parallel Interface Output/Control Register

This register, if PIFEN = ‘1’ in the

register, is used to access a

Smart Panel. A Smart Panel has an integrated controller and frame buffer.

Bit Descriptions:

RSVD:

Reserved - Unknown during read

ESTRT:

Enable Start - Read/Write

The Enable Signal Start Value for the parallel interface

down counter should be written to this field. When the

parallel interface counter counts down to this value during

a write cycle (see RD bit in the

register for write

cycle), the E enable signal on the E pin goes active.

The E enable signal becomes inactive just before the

counter counts down to 0x0, although data remains driven

on the D[7:0] pins throughout the 0x0 count. This allows

data to be driven for one additional clock cycle, providing

data hold time to the Smart Panel.

CNT:

Count - Read/Write

The counter preload value that is written to this field gets

loaded into the parallel interface down counter. When a

write or read cycle is initiated by writing to the RD bit in the

register, the counter begins to count down from

this value.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

ESTRT

CNT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

DAT