Cirrus Logic EP93xx User Manual

Page 783

DS785UM1

27-13

Copyright 2007 Cirrus Logic

IDE Interface

EP93xx User’s Guide

2

7

2

7

27

Default:

0x0000_0000

Definition:

IDE UDMA Configuration Register.

Bit Descriptions:

RSVD:

Reserved. Unknown during read, ignored during write.

RWOP:

Read or write operation selection:

0 - Read

1 - Write.

UEN:

Enable Ultra DMA operation.

1 - to start UDMA

0 - to terminate UDMA by the host.

Note: Before setting the UEN bit to enable UDMA operation:

1 - Set or Clear the RWOP bit to configure for a Write or Read operation.

2 - Perform a dummy read of the IDEUDMAOp register.

3 - Set the UEN bit to enable UDMA operation.

IDEDataOut

Address:

0x800A_0010 - Read/Write

Default:

0x0000_0000

Definition:

In PIO mode write operation, this register is the Output Data Registers,

containing the register contents or the data to be written to the device. The

register is driven onto the DD pins when DIOWn is low. The register is both

read write in this operation. In MDMA and UDMA data-out operations, this

register is an exact copy of the data in the output buffer to be transferred to the

device. The register should only be read in these operations for checking the

output data. Any write in these two operation modes is ignored.

Bit Descriptions:

IDEDD:

IDE output data in PIO writes (read write), data in output

buffer in MDMA and data at the tail of output buffer in

UDMA mode (read only).

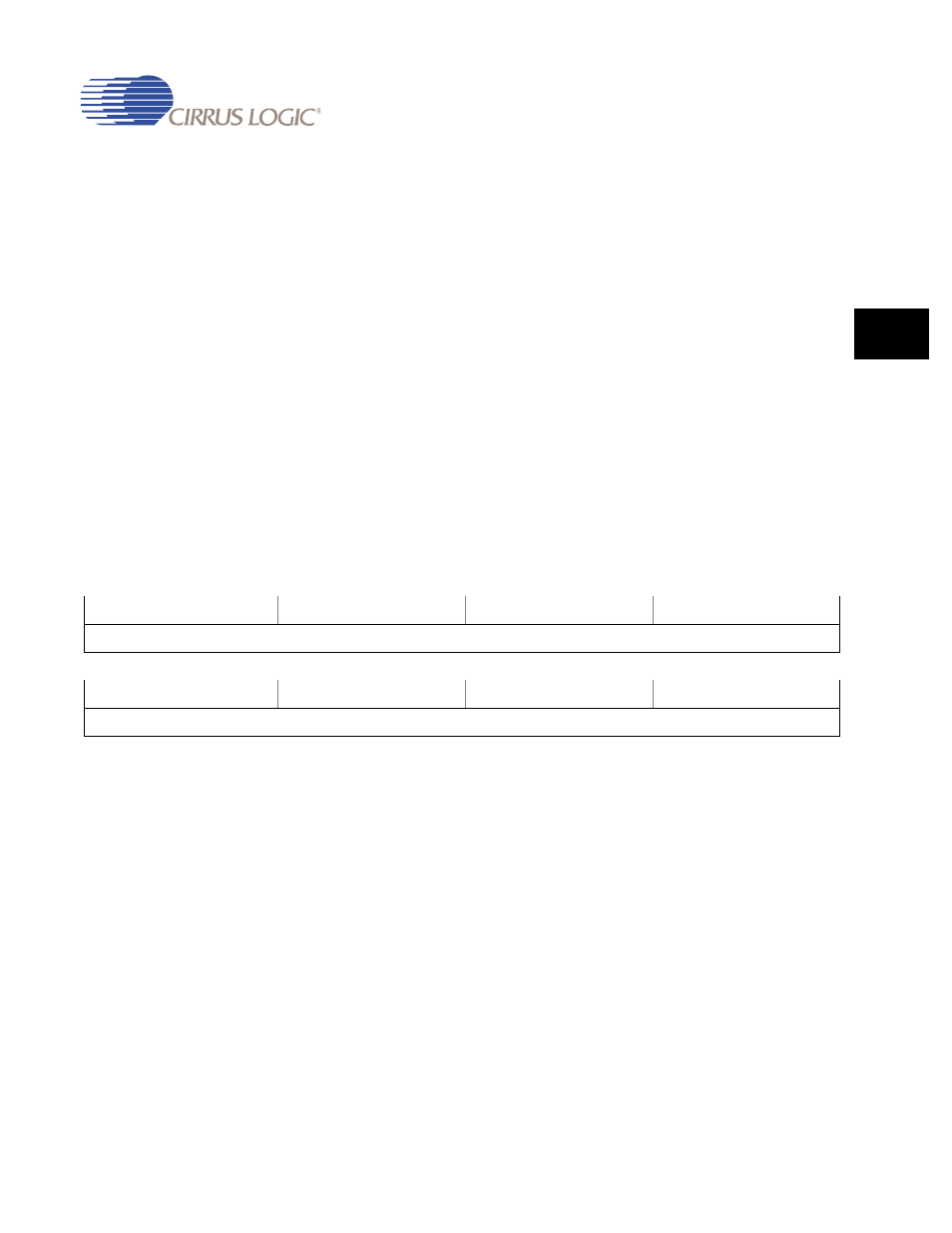

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

IDEDD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

IDEDD