Cirrus Logic EP93xx User Manual

Page 107

DS785UM1

3-37

Copyright 2007 Cirrus Logic

MaverickCrunch Co-Processor

EP93xx User’s Guide

3

3

3

Mnemonic:

CFCMPS

Bit Definitions:

CRn:

First source register

CRm: Second

source

register

Rd:

Destination ARM register. If Rd = 15, destination is ARM

N, C, Z, and V flags.

Compare Double Precision Floating Point

Definition:

Compares two double precision floating point numbers and stores an integer

representing the result in the ARM920T register; the highest four bits of the

integer result match the N, Z, C, and V bits, respectively, in the ARM920T’s

program status register, while the bottom 28 bits are zeros. If Rd = 15, then the

four status bits are stored in the ARM status register, CPSR.

Mnemonic:

CFCMPD

Bit Definitions:

CRn:

First source register

CRm: Second

source

register

Rd:

Destination ARM register. If Rd = 15, destination is ARM

N, C, Z, and V flags.

Compare 32-bit Integers

Definition:

Compares two 32-bit integers and stores an integer representing the result in

the ARM920T register; the highest four bits of the integer result match the N,

Z, C, and V bits, respectively, in the ARM920T’s program status register, while

the bottom 28 bits are zeros. If Rd = 15, then the four status bits are stored in

the ARM status register, CPSR.

Mnemonic:

CFCMP32

Bit Definitions:

CRn:

First source register

CRm: Second

source

register

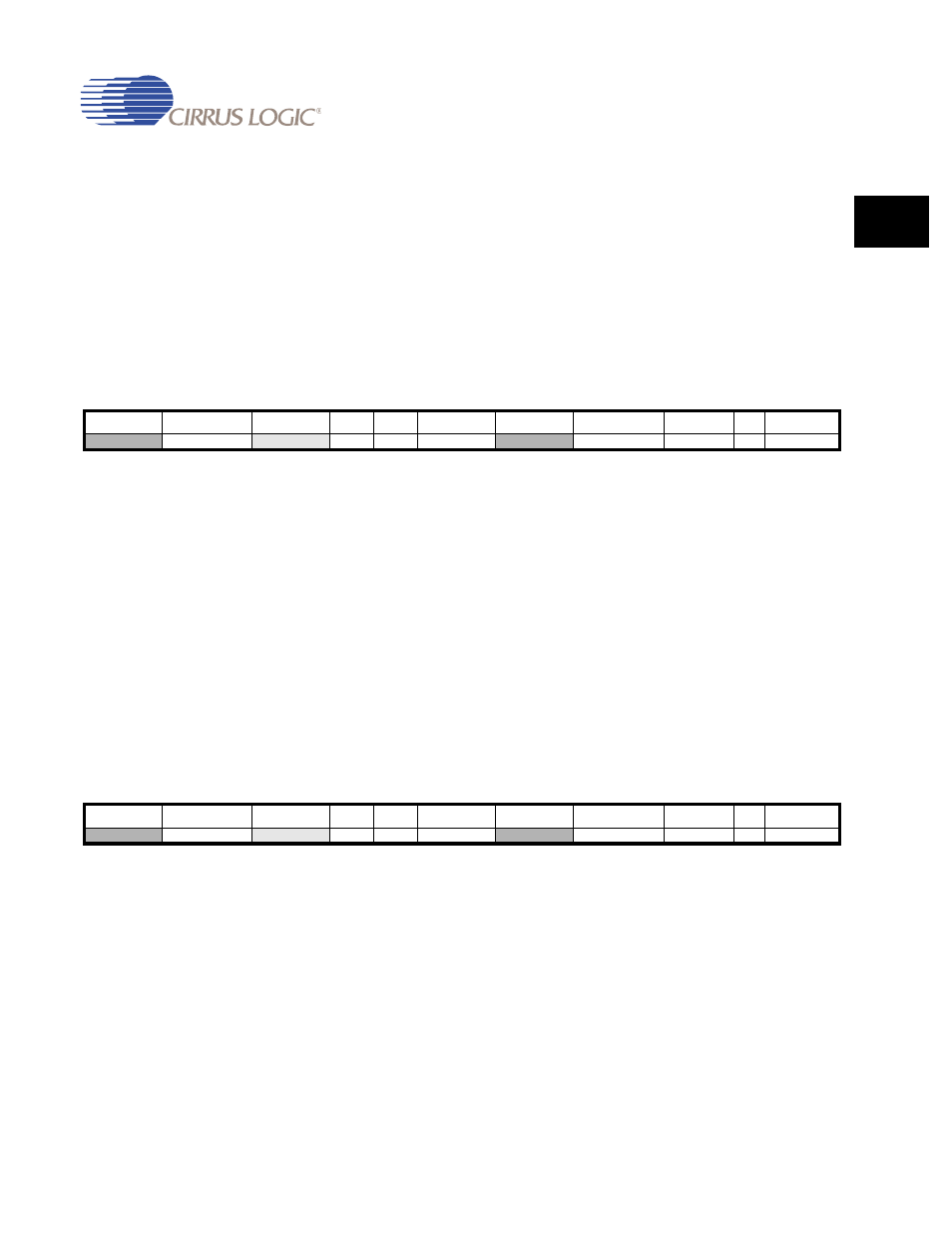

31:28

27:24

23:22

21

20

19:16

15:12

11:8

7:5

4

3:0

cond

1 1 1 0

0 0

0

1

CRn

Rd

0 1 0 0

1 0 1

1

CRm

31:28

27:24

23:22

21

20

19:16

15:12

11:8

7:5

4

3:0

cond

1 1 1 0

0 0

0

1

CRn

Rd

0 1 0 1

1 0 0

1

CRm