Table 5-2. boot configuration options -3, Table 5-2 – Cirrus Logic EP93xx User Manual

Page 129

DS785UM1

5-3

Copyright 2007 Cirrus Logic

System Controller

EP93xx User’s Guide

5

5

5

The normal boot function is described in

Serial boot is functionally identical to normal boot except that the SBoot bit in the SysCfg

register is set. This mode is available for a software configuration option that is readable by

the boot code.

In either normal boot or serial boot mode, once the processor starts up, it will begin to

execute the instruction at logical address 0x0000_0000. Various configuration options are

provided to select a memory device for booting from at address location 0. The options are

listed in

.

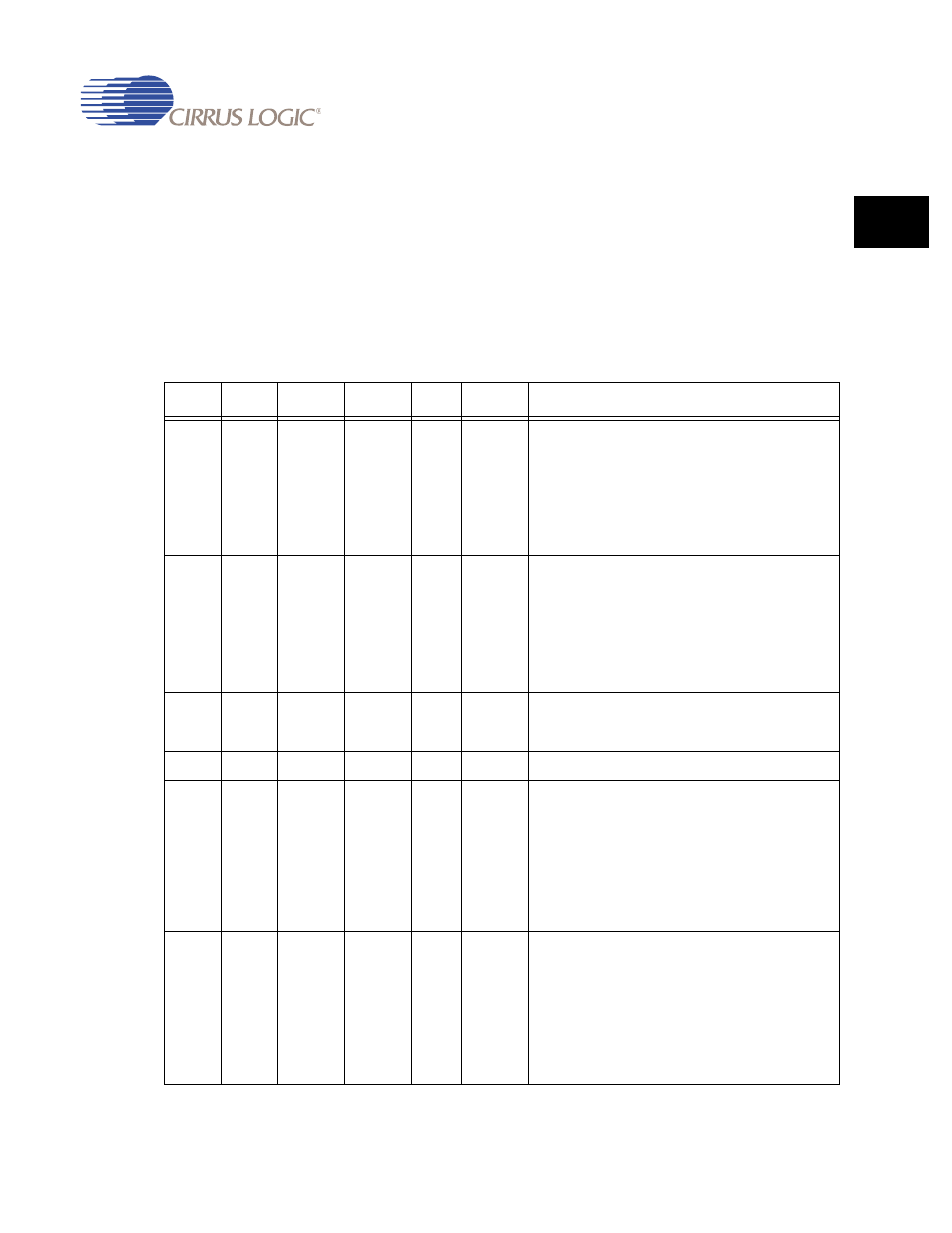

Table 5-2. Boot Configuration Options

EECLK EEDAT

BOOT1

BOOT0

ASDO CSn[7:6]

Boot Configuration

0

1

0

0

1

0 0

0 1

1 0

1 1

External boot fusing Sync boot mode and SDCSn3.

The media type must be either SROM or SyncFLASH.

The selection of the bus width is determined by latched

CSn[7:6]

value:

16-bit

16-bit

32-bit

32-bit

0

1

0

0

0

0 0

0 1

1 0

1 1

External boot using Async boot mode and CSn0. The

selection of the bus width is determined by latched

CSn[7:6]

value:

8-bit

16-bit

32-bit

32-bit

1

1

0

1

x

xx

Internal boot from UART1.

1

1

0

0

x

xx

Internal SPI boot if HeaderID is found.

1

1

0

0

1

0 0

0 1

1 0

1 1

Internal boot using Sync boot mode at the chip select

where the HeaderID exists. The selection of the bus

width is determined by latched CSn[7:6] value:

16-bit

16-bit

32-bit

32-bit

See memory map in

for SYNC

boot mode.

1

1

0

0

0

0 0

0 1

1 0

1 1

Internal boot using Async boot mode at the chip select

where the HeaderID exists. The selection of the bus

width is determined by latched CSn[7:6] value:

8-bit

16-bit

32-bit

32-bit

See memory map in

for

ASYNC boot mode.