Cirrus Logic EP93xx User Manual

Page 709

DS785UM1

22-21

Copyright 2007 Cirrus Logic

AC’97 Controller

EP93xx User’s Guide

2

2

2

2

22

Definition:

End Of Interrupt Register. The AC’97 End Of Interrupt Register is a write-only

register that allows the CODECREADY and WIS interrupts to be cleared. A

write to this location clears the interrupt.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

CODECREADY:

CODECREADY Interrupt Status Clear. A write of “1” to this

location will clear the CODECREADY interrupt bit.

WINT:

Wake-up Interrupt Status Clear. A write of “1” to this

location will clear the WIS interrupt bit.

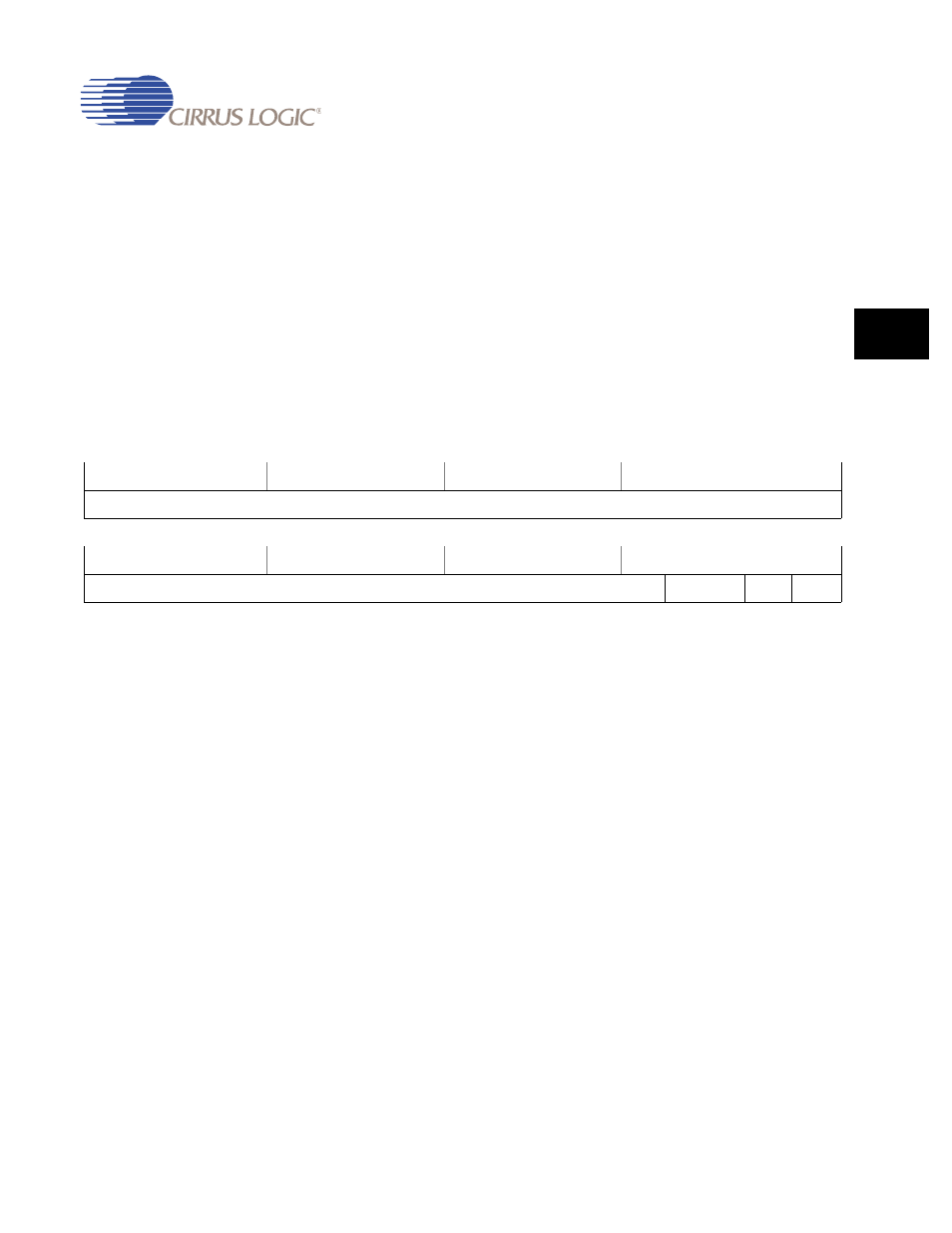

AC97GCR

Address:

0x8088_009C - Read/Write

Definition:

Global Control Register. The AC97GCR register is the main control register for

the AC’97 Controller. All bits are cleared on reset.

The AC97IFE creates the clock enable signal for the clock controller block. It

is used to enable/disable both PCLK and AC97LK.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

OCODECReady:

If set to “1”, this bit will override normal CODEC-ready

definition.

LOOP:

Loopback mode: If this is set to “1”, loopback test mode is

enabled. Defaults to “0” when reset. Ensure this bit

is always “0” for normal operation.

AC97IFE:

AC97IF Enable: If this bit is set the AC’97 is enabled.

Defaults to “0” on reset. When set to “0”, all FIFOs

are reset to “0”.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

OCODECReady

LOOP

AC97IFE