Cirrus Logic EP93xx User Manual

Page 570

15-12

DS785UM1

Copyright 2007 Cirrus Logic

UART2

EP93xx User’s Guide

1

5

1

5

15

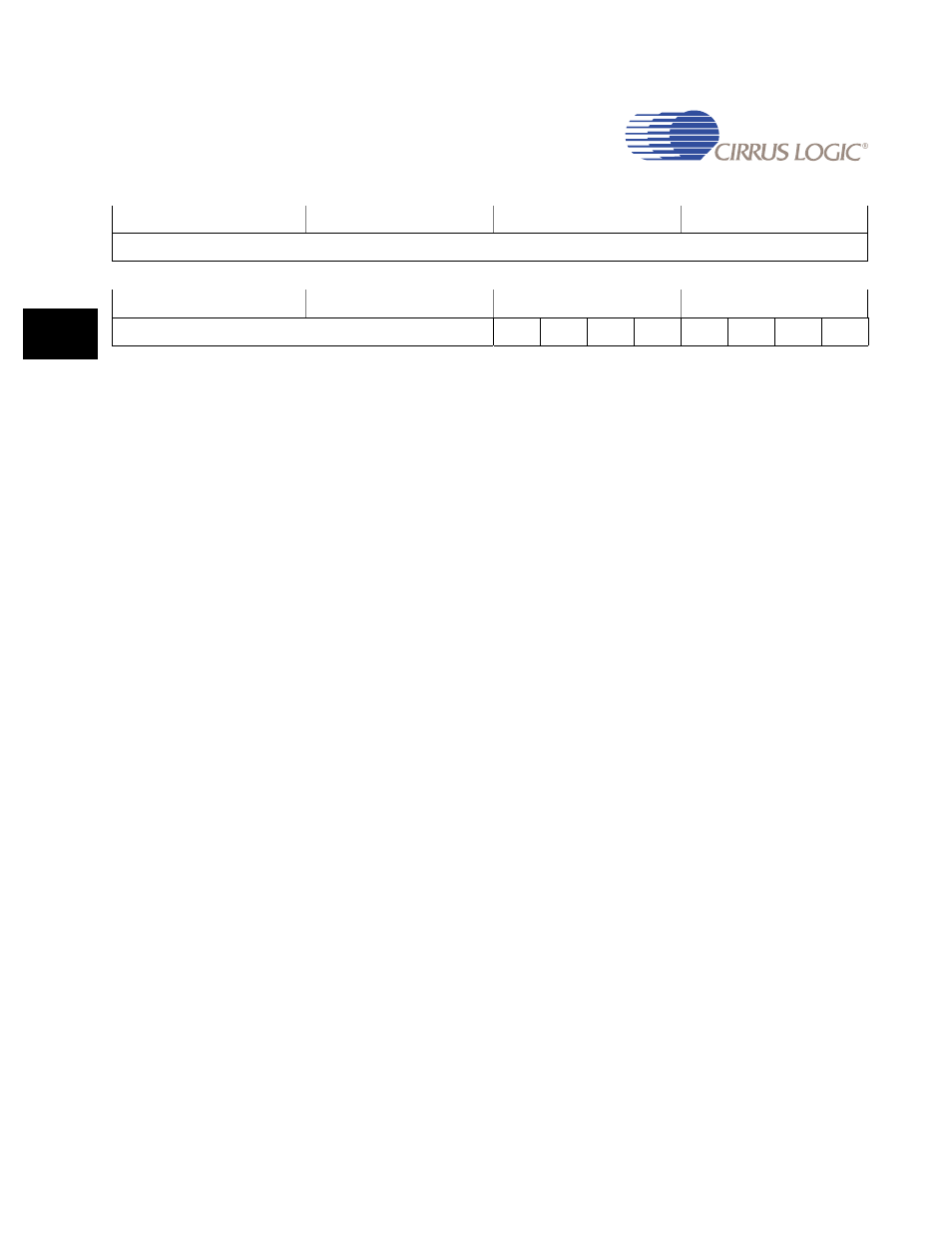

UART2Ctrl

Address:

0x808D_0014 - Read/Write

Default:

0x0000_0000

Definition:

UART Control Register

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

LBE:

Loopback Enable, for SIR and UART only.

1 - If the SIR Enable bit is also set to “1”, and register

UART2TMR bit 1 (SIRTEST) is set to “1”, the SIR output

path is inverted and fed through to the SIR input path. The

SIRTEST bit in the test register must be set to “1” to

override the normal half-duplex SIR operation. This should

be the requirement for accessing the test registers during

normal operation, and SIRTEST must be cleared to “0”

when loopback testing is finished. This feature reduces the

amount of external coupling required during system test.

0 - This bit is cleared to “0” on reset, which disables the

loopback mode.

RTIE:

Receive Timeout Enable. If this bit is set to “1”, the receive

timeout interrupt is enabled.

TIE:

Transmit Interrupt Enable. If this bit is set to “1”, the

transmit interrupt is enabled.

RIE:

Receive Interrupt Enable. If this bit is set to “1”, the receive

interrupt is enabled.

MSIE:

Modem Status Interrupt Enable. If this bit is set to “1”, the

modem status interrupt is enabled.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

LBE

RTIE

TIE

RIE

MSIE

SIRLP

SIREN

UARTE